- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- Re: HRESET_B Problem in Power On Reset Sequence

HRESET_B Problem in Power On Reset Sequence

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SIr,

I am using a custom made T1042 based card. I am having problem in one card because of power on sequence of the card. A CPLD is used to follow the power on sequence. As a start when I pull down the PORESET_B signal, then according to power-on reset sequence that is mentioned in Figure 4-1 of reference manual, HRESET_B should also get pull down but this is not happening. HRESET_B is continuously on HIGH state resulting not following POWER on sequence. Hence ASLEEP LED is always on. What might be the issue and the solution to this problem?

I have other boards also with same design but they are not causing this issue with same CPLD Code.

Regards,

Ather

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to the processor's Data Sheet and Design Checklist to ensure that it is connected and powered correctly.

Also it could be useful to refer to the T1042D4RDB design data available at:

https://www.nxp.com/downloads/en/printed-circuit-boards/T1042D4RDB-PA_DF.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks UFedor for your help.

I am using hard-coded RCW settings.

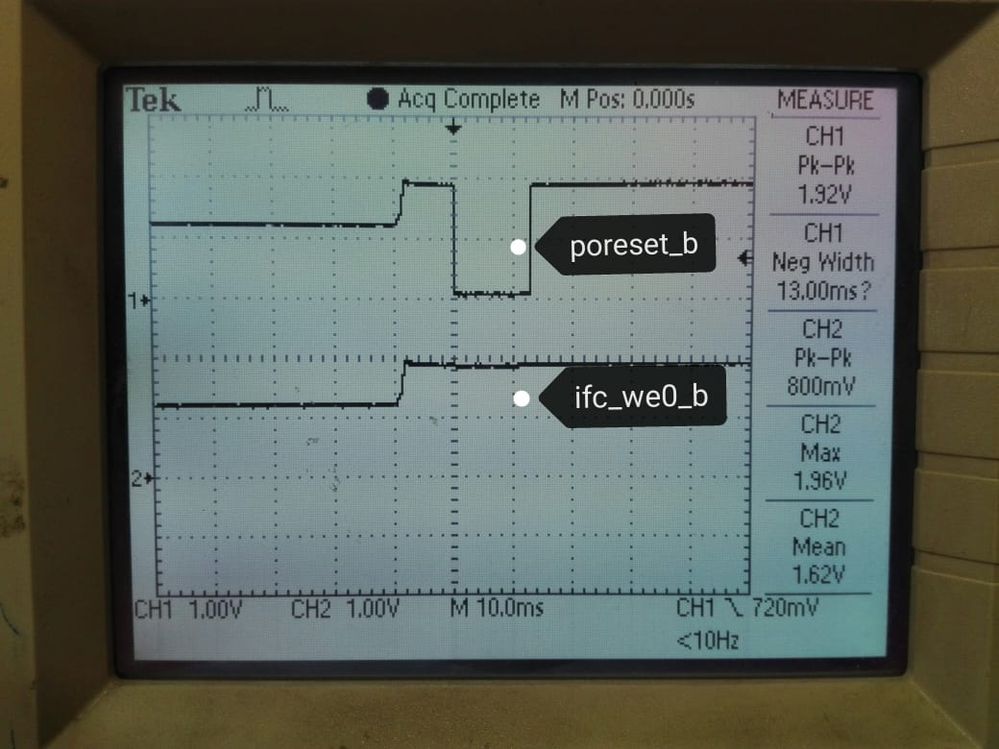

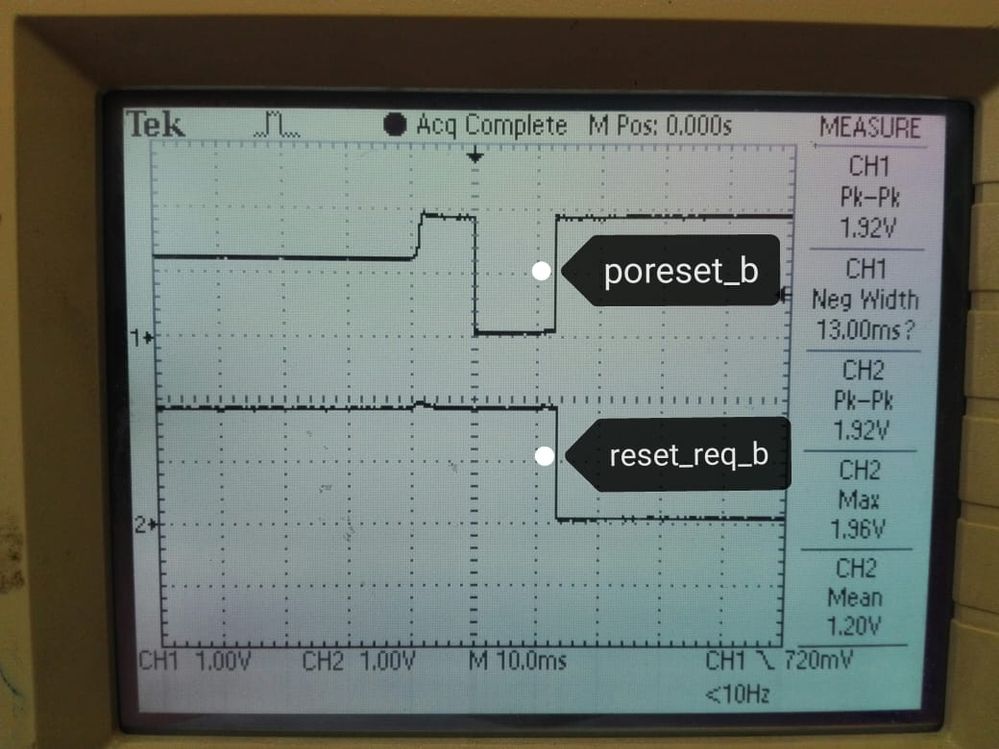

Following are the waveforms of signals with respect to PORESET_B.

Upper signal is PORESET_B and the trigger of the scope is set on the falling edge of this signal. The other wave is HRESET_B in first picture and RESET_REQ_B in the later one.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How SYSCLK is applied?

What is the IFC_WE0_B voltage?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

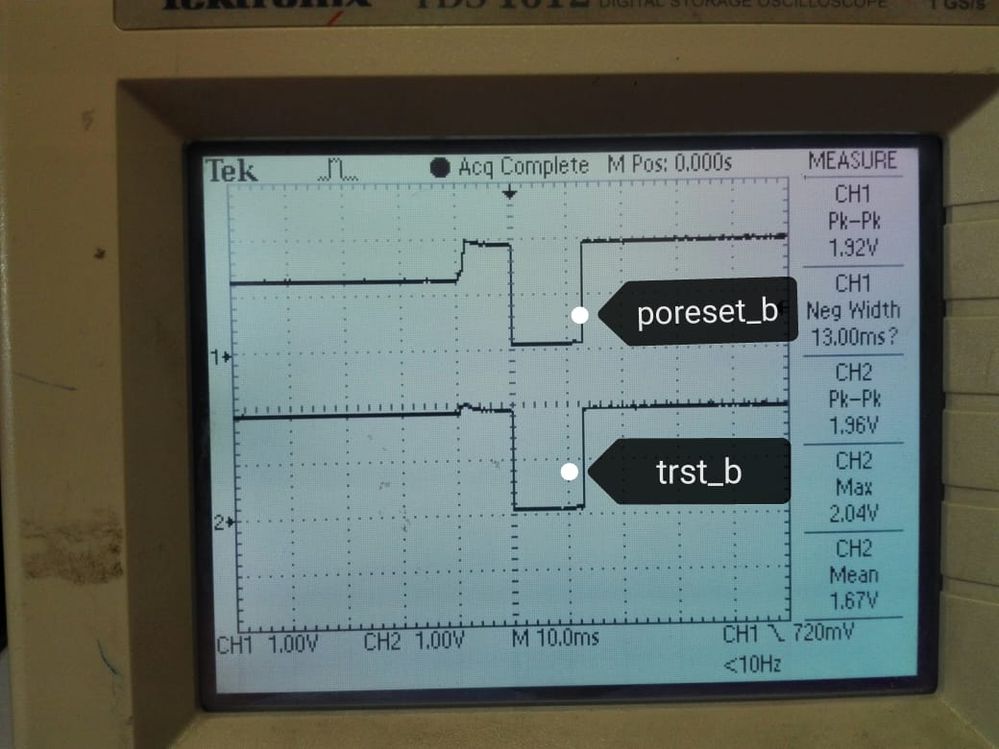

Please confirm that TRST_B is asserted during POR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes TRST_B is also asserted alongwith poreset_b

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to the processor's Data Sheet and Design Checklist to ensure that it is connected and powered correctly.

Also it could be useful to refer to the T1042D4RDB design data available at:

https://www.nxp.com/downloads/en/printed-circuit-boards/T1042D4RDB-PA_DF.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @Ufedor for your help.

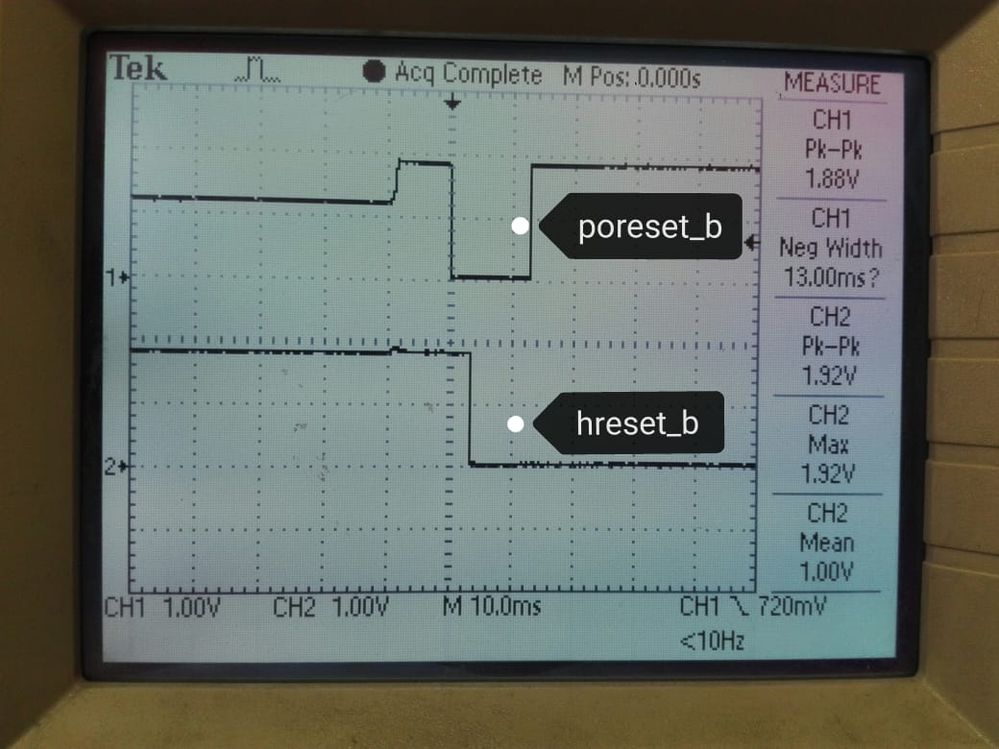

As per your suggestion, I checked powers of the board and came to know that VCORE was not proper. So after resolving the issue in the power, scenarios of HRESET_B and RESET_REQ_B are changed.

Now HRESET_B gets low after PORESET_B but does not pull high after PORESET_B gets high.

Following are the updated pictures of the signals.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the RCW source?

Please ensure that valid RCW is provided during POR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hard-coded RCW setting is being used.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please consider that SerDes PLLs are not powered down and 125 MHz reference clocks have to be applied.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks ufedor for your help and your precious time.

My board is now in working state. The problem that I identified is that due to faulty TTL to MAX232 coverter IC , I was always receiving high on RX of Debug UART. Hence it was not following Power on reset sequence. Apparently this should not be an issue so I overlooked it previously. But when I disconnected the RX signal from MAX232 IC, the board is now powering up properly.

Would you please comment on this issue because my other boards also don't follow power on reset sequence when TTL UART is connected to the board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the significance of UART1_SIN & UART1_SOUT in reset sequence?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

> when TTL UART is connected to the board.

What do you mean?

What is the corresponding connection schematics?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using USB to TTL converter for debug UART and I have this directly to processor pins UART1_SIN and UART1_SOUT.

Please see this link for reference https://www.adafruit.com/product/954 .

Connection detail is as follows.

Wire of Cable Pin of T1042

GND GND

RX UART1_SOUT

TX UART_SIN

Power Not connected

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Provided problem description lacks technical details.

Please provide a digital scope trace showing all reset signals behaviour.

Also, what is the RCW source and does it contain a valid RCW?