- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

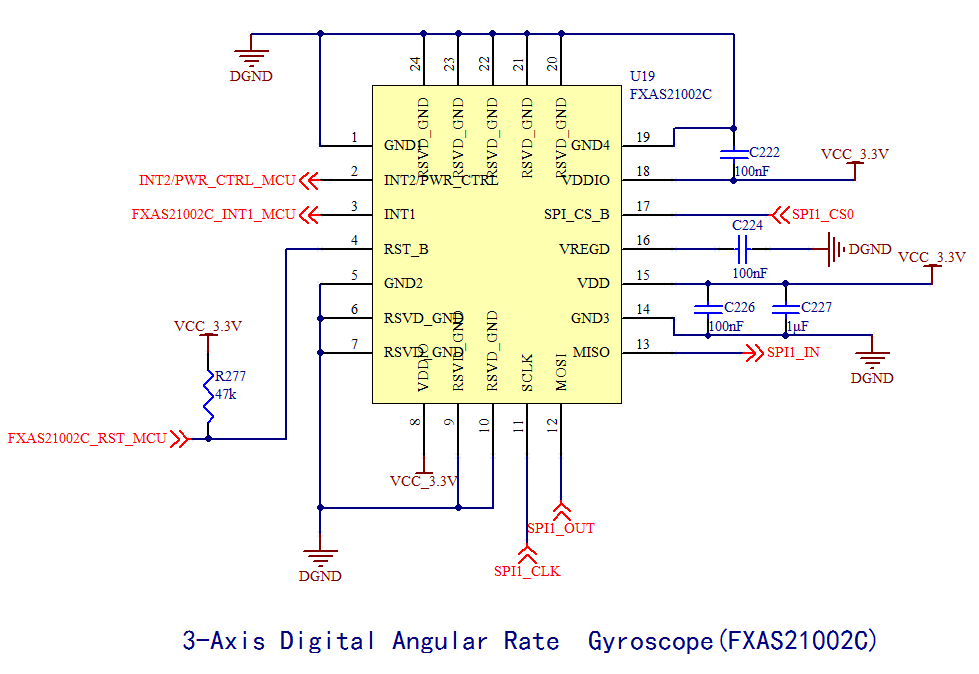

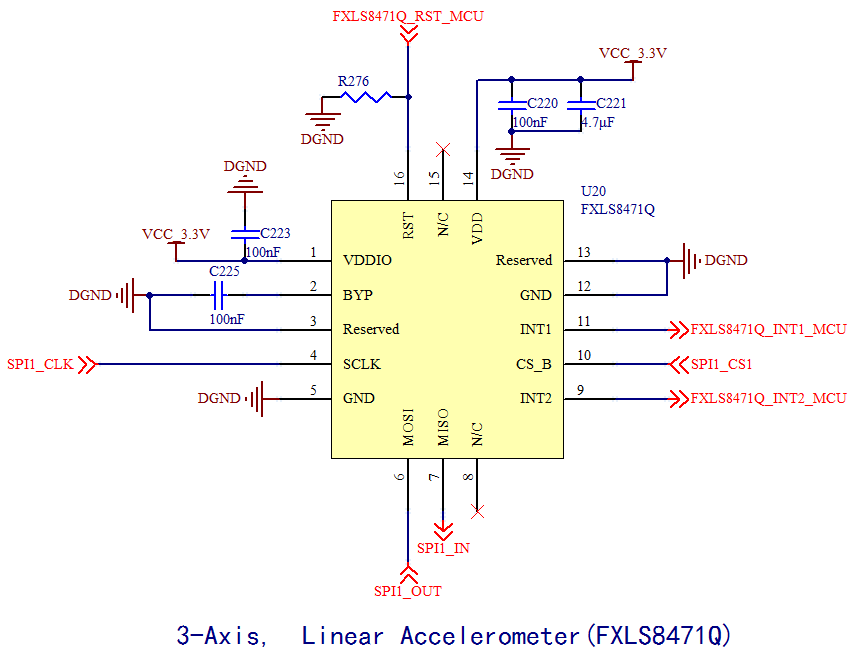

FXAS21002C—MISO Pin Question

Hello ,

I encounter a problem when I connect FXLS8471Q and FXAS21002C on the same SPI. The detailed schematic is shown below. Now, the comunication between FXAS21002C and the master is normal. But the comunication between FXLS8471Q and the master is not normal, no matter the FXAS21002C on 3-wire or 4-wire mode. I guess that the MISO pin of FXAS21002C has effect on the MISO pin of FXLS8471Q. The datasheet of FXAS21002C describes that In 4-wire SPI mode the MISO pin is always placed in a high impedance state when CS_B is not asserted (logic high level) and when FXAS21002C is operated in 3-wire SPI mode - bysetting CTRL_REG0[SPIW] = 1 - the SA0/MISO pin is always placed in a high impedance (high-z) state. I want to know how much resistance of the high impedance is.

Best regards,

Ben

Hello Ben,

This sounds like a known SPI issue described in the FXAS21002CER including possible workarounds.

Hope it helps.

Best regards,

Tomas