- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: pcssck

pcssck

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

pcssck

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Target is S32K148.

I'm trying to do an SPI transfer consisting of 5 bytes(40 bits) where the CS is asserted for the duration of transfer. The baud rate is 4mhz, peripheral Clock is PLL and Divider is 1 and peripheral Clock frequency is 40mhz , using SPI0 for this I have the following in LPSPI0_CCR:

SCKDIV 0X08

DBT 0X04

PCSSCK 0X03

SCKPCS 0X03

Using these values results in an uneven clock and longer CS assertion period. when I twig these parameters the clock changes but I am not able to achieve the desired symmetrical with desired CS AASERTION DURATION OF 10 US. please look at attachment for the Screenshot

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I understand the asymmetricity is in the SCK-to-PCS Delay / PCS-to-SCK Delay.

But this can't be seen in the screenshot.

Can you measure it with an oscilloscope and an active probe?

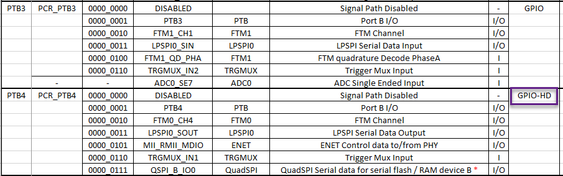

Do you use the High-Drive pins? PCR[DSE] = 1.

S32K148 IO_Signal_Description_Input_Multiplexing.xlsx

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for your quick response,

In the screen shot the clock(red color) is not a%50 duty signal, Can't you see that?

when you say:

"I understand the asymmetricity is in the SCK-to-PCS Delay / PCS-to-SCK Delay"

You mean there are not the same?

Yes they are not the same.

I will measure it and I use hi drive pins for the clock signal and let you know.

Thanks,

Koorosh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Koorosh,

If you mean the 74.63% duty, it is not given by the SCK-to-PCS, PCS-to-SCK delays.

For example, PCS-to-SCK is just the delay from the PCS assertion to the first SCK edge.

The 35.6us delay is most likely caused by the CPU overhead.

The SW must prepare another 40b transfer and it takes some time.

Regards,

Daniel