- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Why does s32k144 take more time to run code in ram?

Hello!

I have a problem. I test some codes, When s32k144 runs these codes in ram, It takes more time. And when s32k144 runs code in flash, It take less time.In my opinion, the result must be reversed. So I am confused。

My IDE: WIN10_64 + IAR 7.60.2 for ARM

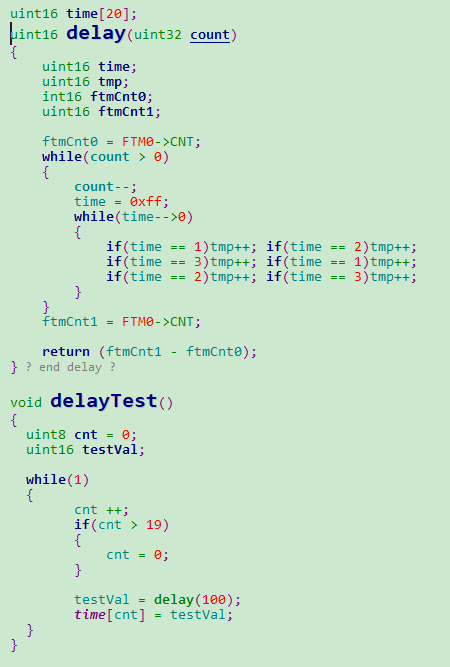

And my codes are these:

delay() function returns the executive time of "while(count > 0)". And then the array "time" stores the executive time. delayTest() function calls delay() function continuously。

example 1:

The codes of delay() function are in flash. And the codes of delayTest() function are in flash.

the average value of the array time is 2820.

example 2:

The codes of delay() function are in ram. And the codes of delayTest() function are in flash.

the average value of the array time is 3220.

example 3:

The codes of delay() function are in flash. And the codes of delayTest() function are in ram.

the average value of the array time is 3700.

I hope someone could help me.

Best regards to you!

Thanks!

Hello,

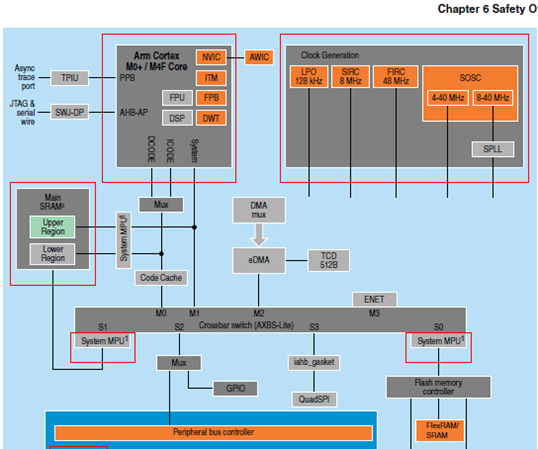

Which SRAM region do you use?

You should get the best results when you use SRAM_L for code and SRAM_U for data.

Please see below.

Regards,

Daniel

Hi, Daniel

Thank you for you reply. It's very useful to me.

I place the delay() function and delayTest() function in SRAM_U. Then I will test these functions in SRAM_L.

And I place global variable in SRAM_L. So the access efficiency of data in SRAM_L will be lower than the access efficiency of data in SRAM_U?

Best Regards

Chen

Hi Chen,

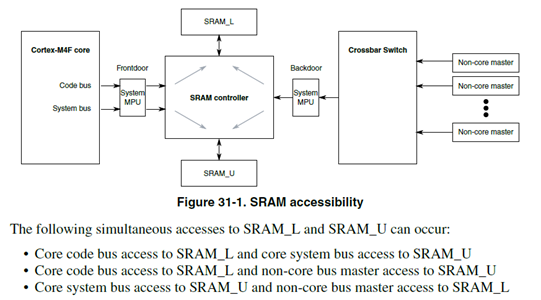

The core has zero-wait-state access to both instructions and data in SRAM_L region via Processor Code (PC) bus.

But as the bus name imply, normal operation has code accesses on the PC bus and data accesses on the Processor System (PS) bus (Section 33.2.1, RM rev.8).

This allows simultaneous core accesses to both instructions and data and provides better performance.

Regards,

Daniel