- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all,

I was hoping someone could shed some light on some odd behaviour.

My code is as follows:

void LpTimerInit(void)

{

/*

DBG_EN = 1

DOZE_EN = 1

SW_RST = 1

M_CEN = 1

*/

LPIT0->MCR = 0x0000000F;

/*

"Before clearing the Software Reset bit, software must wait for 4

peripheral clocks (for clock synchronization and reset propagation)."

CPU clock is 80 MHz. SOSCDIV2_CLK is 1 MHz.

80 MHz / 1 MHz = 80 per clock tick. 80 * 4 clock ticks = 320.

*/

for (uint32_t i = 0; i < 320; i++)

{

/*

Intentionally empty.

Yes, this is more than 320 instructions, but this is a lazy/easy way to wait for long enough.

Make sure code is not optimized away.

*/

}

/*

SW_RST = 0: abort reset.

*/

LPIT0->MCR &= ~0x00000002;

/*

Not sure if we need to wait *after* clearing reset, but if there is

a propagation delay for making reset high, then there might be one for

making reset low as well.

*/

for (uint32_t i = 0; i < 320; i++)

{

/* Intentionally empty. */

}

/*

TRG_SEL = 0

TRG_src=0

TROT = 0

TSOI = 0

TSOT = 0

Mode = 00

CHAIN = 0

T_EN = 0

*/

LPIT0->TMR[0].TCTRL = 0x00000000;

LPIT0->TMR[1].TCTRL = 0x00000000;

LPIT0->TMR[0].TVAL = 1000000;

/* Just for testing. Will, of course, get a different value. */

LPIT0->TMR[1].TVAL = 1000000;

/*

TIE0 = 1: Interrupt request on channel 0

*/

LPIT0->MIER = 0x00000001;

/*

Interrupt LPIT Ch0 enabled in NVIC.

*/

enableInterrupt(LPIT0_Ch0_IRQn);

/*

Start channels 0 and 1 simultaneously.

*/

LPIT0->SETTEN = 0x00000003;

}

Other details about the setup:

I'm using an 8 MHz crystal on SOSC. I'm feeding SOSC into the SPLL to generate a 160 MHz SPLL_CLK, which is divided down to an 80 MHz CORE_CLK. I divide SOSC down to a 1 MHz SOSCDIV2_CLK, which feeds the functional clock of the LPIT.

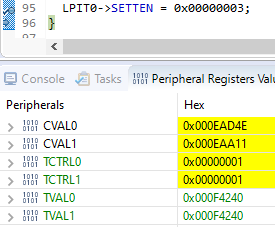

Everything works as expected. I can generate the 1s interrupt through ch0. However, immediately after executing the last line in the code, there is already a time difference between Ch0 and Ch1. See the following:

I have verified that before executing the statement, CVAL0 and CVAL1 are both still 0xFFFFFFFF. TVAL0 and TVAL1 are loaded correctly.

The time difference always comes down to 829 microseconds, and stays constant after this initial offset. This is almost a whole millisecond. I thought that setting the timers with SETTEN would cause them to start simultaneously. What could cause this behaviour I'm seeing?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi jh2,

Have you tried the suggestions in S32K1xx MCU Family - Reference Manual ?

"While the timer is running, CVALn register reads may not return the real value. If the timer value needs to be read, read it during an LPIT interrupt service routine."

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi jh2,

Have you tried the suggestions in S32K1xx MCU Family - Reference Manual ?

"While the timer is running, CVALn register reads may not return the real value. If the timer value needs to be read, read it during an LPIT interrupt service routine."

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you. We use the S32K146. I missed the W suffix, and thought I was in the clear.

Since we need to poll the timer for exact microseconds, I'd rather not use an interrupt. I think we'll have to use the FTM for that.