- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

Hi,

Pre-Information:

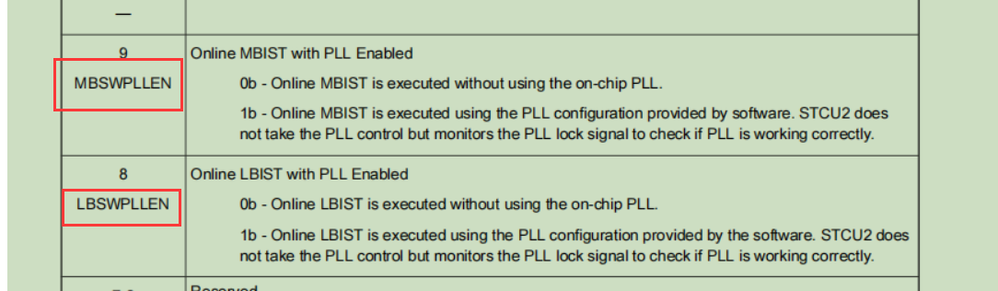

In the "safety->STCU2" section of S32K3XXRM, there is a register related to PLL monitoring located at STCU2->RUNSW. According to the description, when our clock configuration uses PLL, we need to enable these two fields.

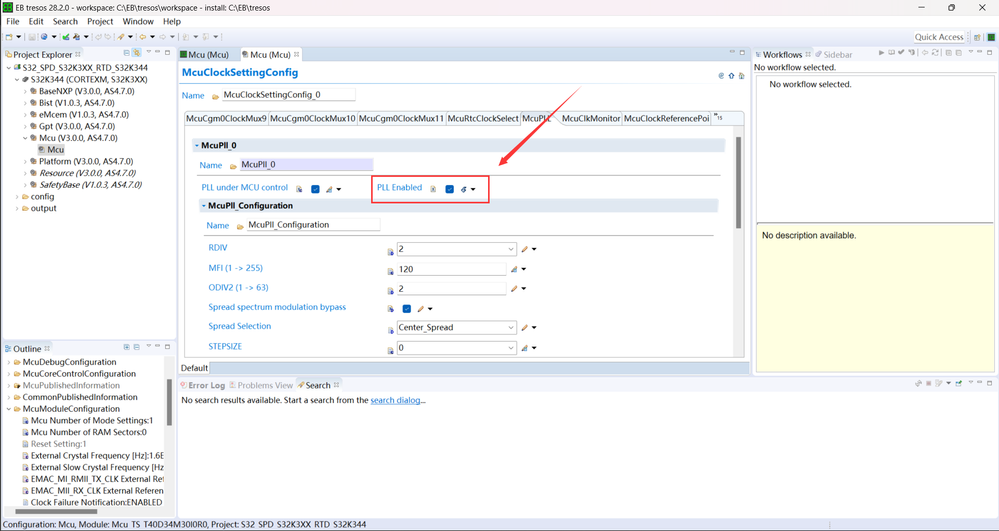

In the demo provided by S32K3 Safety Peripheral Drivers version 1.0.3 Design : Product Download : Files (flexnetoperations.com), PLL is enabled.

Based on the above information, these two bits should be set to 1 in the STCU2->RUNSW register in the demo.

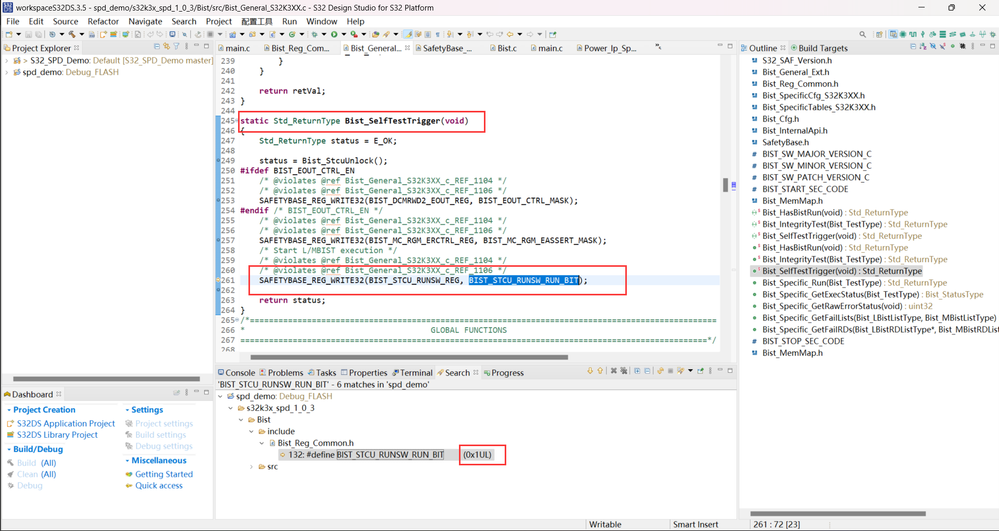

And in the main.c file of the provided demo, the place where this register is set is in BIST_RUN()->Bist_Specific_Run()->Bist_SelfTestTrigger()->SAFETYBASE_REG_WRITE32(BIST_STCU_RUNSW_REG, BIST_STCU_RUNSW_RUN_BIT);

However, in the case where PLL is enabled in the clock configuration, the library driver provided by SPD does not set these two bits to 1.

1. Is this a design flaw or do users need to manually modify certain code?

已解决! 转到解答。

Hello,

1. Is this a design flaw or do users need to manually modify certain code?

Well, this would be the question to designers of the SW. But for sure if you want run the PLL for BIST, you need to set those bits.

If you like the feedback from SW owners, please submit a ticket at NXP.com so it will reach them.

Best regards,

Peter

Hello,

1. Is this a design flaw or do users need to manually modify certain code?

Well, this would be the question to designers of the SW. But for sure if you want run the PLL for BIST, you need to set those bits.

If you like the feedback from SW owners, please submit a ticket at NXP.com so it will reach them.

Best regards,

Peter