- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32k148 - SAI FIFOs

S32k148 - SAI FIFOs

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32k148 - SAI FIFOs

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using s32k148 chip. When reading the SAI Rx FIFOs, I am getting pointer values greater than 7.

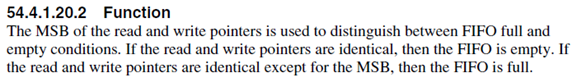

The S32K Reference Manual specifies, that each receive channel has a FIFO of 8 units (each unit 32-bit size). The manual also specifies, that in SAI RFRn register WFP and RFP have 4-bit size, which is more than required to store 0-7 write/read pointer.

Are the FIFOs bigger than 8 units? Is it normal to observe Rx WFP values larger than 7?

Thank you,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hai jakub,

could you please tell me which microphone have you used for SM32K148 ??

if possible could you share the details, how to configuration microphone ??

Thanks

saichand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Saichand,

I did not use a microphone. I soldered a wire to loopback SAI0_D0 (tx) to SAI0_D2 (rx).

Thanks,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You write that you are getting pointer value > 7.

What exact values do you get?

You should get 0b1000 for sure since the FIFO size is 8.

Thanks,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

I am getting values from 0 to 10 (did not check if higher as well).

Thanks,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jakub,

Sorry for the delay.

We have been trying to reproduce that without any success.

The FIFO pointers show values in the range 0-8 as expected.

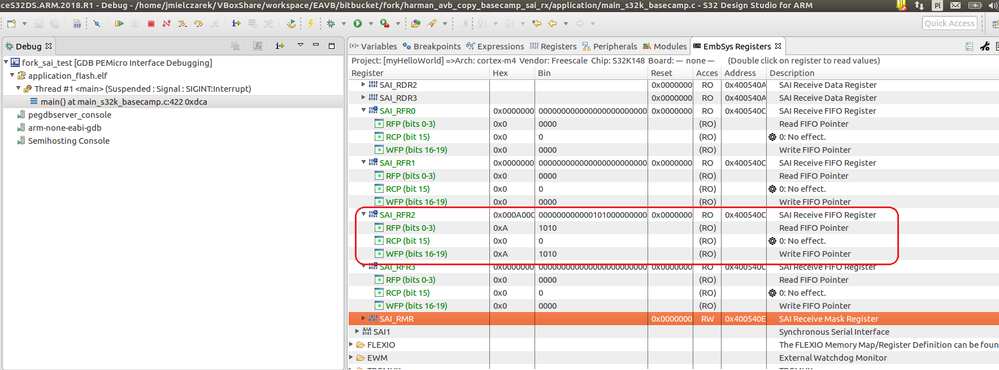

Could you share a screenshot of the registers with the FIFO pointers?

Also, what SAI configuration do you use?

The more information, the better.

The SAI initialization code or a test project would be great.

Thanks,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let me add that on my board SAI0_D0 output is wired to SAI0_D2 input.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jakub,

Thanks for the additional information and sorry for the delay.

Unfortunately, the issue is still under discussion with design.

Also, we have still difficulties to reproduce the bahaviour for some reason.

If possible, could you share a working test code, the whole project?

You could send it via a ticket if you don't want to post it here.

Anyway, I will update this thread once we have confirmation from the IP designer.

Thanks,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniel,

I don't have a sample project which I could share. I only have my full application.

Would register dump from S32 Design Studio help? If yes, then I can post one, just let me know which registers you need.

Thanks,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jakub,

UPDATE,

I'm sorry for the delayed response and confusing information.

The FIFO pointers are circular. Although the FIFO size is 8 words, the pointers increment up to 0xF.

The number of words in the FIFO is then the relative difference between the WFP, RFP pointers.

Let say 5 words is written to the Receive FIFO by the HW, then, the RFRn_WFP pointer shows 0x5 while the RFRn_RFP pointer shows 0x0 until all the data are read (by DMA, for example) from the FIFO, then the RFRn_RFP is also 0x5.

And because at this point the pointers are identical, the FIFO is empty.

If other 5 words are received, the RFRn_WFP pointer increments to 0xA while the RFRn_RFP pointer stays at 0x5 until the data (5 words) are read from the FIFO, then the RFRn_RFP also increments to 0xA.

And because at this point the pointers are identical, the FIFO is empty again and a new transfer can be initialized.

This is a correction of my previous answer - the FIFO does not need to be reset. I’m sorry for that.

You can refer to the sai_transfer_s32k148 SDK example, this example utilizes DMA.

The FIFOs are reset during initialization in the SAI_DRV_RxInit(), SAI_DRV_TxInit() funtions only.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thank you for your update and explanations.

I think we can close this thread.

Regards,

Jakub

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniel,

Thank you for the answer.

One question: if DMA is used to read data from SAI (in RX mode), do the FIFO pointers still need to be reset, if yes, when?

Regards,

Jakub