- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K312 sCheck to open the ECC test, run the sCheck_CortexM7_ErrRead function to enter the hardf

S32K312 sCheck to open the ECC test, run the sCheck_CortexM7_ErrRead function to enter the hardfault

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K312 sCheck to open the ECC test, run the sCheck_CortexM7_ErrRead function to enter the hardfault

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

S32K312 sCheck to open the ECC test, run the sCheck_CortexM7_ErrRead function to enter the hardfault.

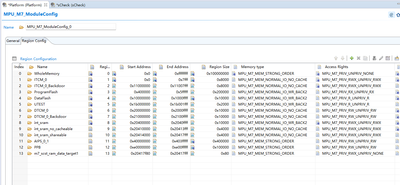

According to the description in the S32K3_SAF_SCHECK_UM.pdf, the ramcode_no_cacheable segment has been placed in the Ram region, but the assignment of a local variable in the sCheck_CortexM7_ErrRead function will trigger a Hardfault. This address has been configured in the MPU to execute code, what is the possible reason here?

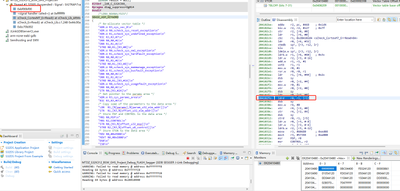

Before running uint64 result=0ULL;

After running uint64 result=0ULL

Is there any way to troubleshoot this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Yongxingjia,

What is the address of the result variable?

What do you see in the MMAR register? (MMARVALID = 1)

It detects a fault exception on a write, not code execution.

I see several regions overlapping, is it intended?

Did you enable sub-regions in that regions.

Also, the base address of a region should be aligned to the size of the region. For example, a 64KB region must be aligned on a multiple of 64KB, for example, at 0x00010000 or 0x00020000. I don't see that in your MPU configuration.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,Daniel:

I configured it with reference to the demo of the S32K344,and the demo also overlapping it.

Now I've also modified the configuration of the MPU, but I'm getting a new problem

When "204102c2: str r2, [r0, #0]"is executed in the sCheck_CortexM7_ErrRead function, the vector table is relocated to the 0x20410480, 0x20410480 the storage is the 0xBF00BF00

When 204102fe: ldrd r0, r1, [r1] is executed in the sCheck_CortexM7_ErrRead function, the code executes exceptionally

What are the precautions about ECC in the sCheck integration, ECC-related testing and debugging have been for a long time, and there has been no progress, and the user manual is not very clear, or can you provide a S32K312 Demo project for reference, thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Yongxingjia ,

please could you:

- specify which sCheck test exactly causing this issue?

- find out the address for these symbols: "sys_stack_init", "sys_vec_0"

- which compiler are you using?

Kind Regards,

Radoslav