- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K312 Pad-Level during wakeup

S32K312 Pad-Level during wakeup

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

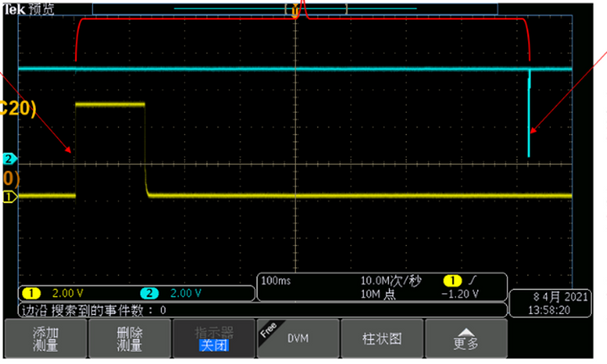

When I used the K312 chip to test the Wakeup function, I found that the GPIO output by OutPut can maintain a high level output after entering standby, but it will become a low level after wakeup.

Here is my setup:

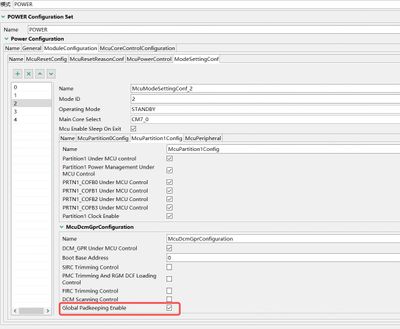

1. Use the DS tool to select [Global Padkeeping Enable] under StandByMode in the Power component, and set the [Pad keep enable] option of the GPIO used in the pin component to Enable.

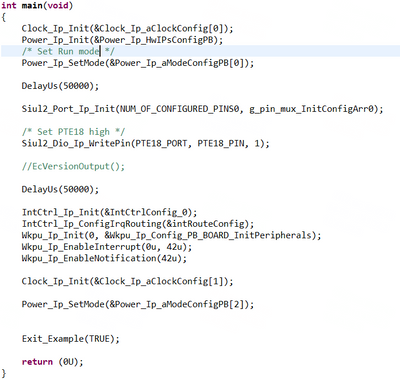

2. In the case of setting the above PadKeeping, initialize GPIO in Main and set high level output

3. Call the function Power_Ip_SetMode to enter StandBy

How can I keep the high level of the output terminal during wakeup?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't think this is a problem.

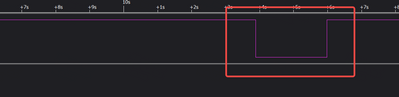

This picture is not very clear and I have highlighted the important place for your obervation, as you can see, the level here is also pulled down.

the reason it say in picture conclusion.

"When waking up from standby mode, HSE non-secure boot will cost 1.8ms,the startup code(from reset_handler to main) will cost 4.3ms, Clock_Ip_Init will cost 830ms(Optimization level -O0). When enabling padkeeping, you can make sure the IO voltage will retain the setting in run mode during these 3 periods of time, until you disable the padkeeping and reset the port after waking up."

After your program enters the main function, it initializes the PORT after a delay, and then pulls it high

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Senlent

I use DS configured as follows:

1. In the pin tool, configure PTE18 as Pad keep enable, which corresponds to PKE in SIUL2_MSRC, and set it during PortInit

2. In the Power component, select Global Padkeeping Enable, which corresponds to STANDBY_IO_CONFIG in DCMRWF1, which is set by calling the function Power_Ip_SetMode when entering StandBy

The process in the Main function is as shown in the picture below, but after wakeup, PTE18 will still be pulled down

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't think this is a problem.

This picture is not very clear and I have highlighted the important place for your obervation, as you can see, the level here is also pulled down.

the reason it say in picture conclusion.

"When waking up from standby mode, HSE non-secure boot will cost 1.8ms,the startup code(from reset_handler to main) will cost 4.3ms, Clock_Ip_Init will cost 830ms(Optimization level -O0). When enabling padkeeping, you can make sure the IO voltage will retain the setting in run mode during these 3 periods of time, until you disable the padkeeping and reset the port after waking up."

After your program enters the main function, it initializes the PORT after a delay, and then pulls it high

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Senlent

Thank you for your answer, I still have one thing I don't understand: what is the action after wakeup or the pad level is pulled down due to the function I called? Is it caused by writing 1 to the STANDBY_IO_CONFIG bit in the register DCMRWF1? Can this drop be avoided?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can't think of a better way to solve your application requirements.

If you want it to be always in a high state, why not directly use an external circuit to pull up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Senlent

Based on your answer above, I understand that after wakeup, the port will be reset only when the STANDBY_IO_CONFIG bit 1 in DCMRWF1 is set. So if the port is initialized and set to a high level before setting DCMRWF1, will this high level be maintained?

I did this test and found that this solution can keep the port high.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1.So if the port is initialized and set to a high level before setting DCMRWF1, will this high level be maintained?

If you enable padkeeping before going to standby mode(write DCM_GPR->DCMRWF1[STANDBY_IO_CONFIG] = 0. Which is default register value no matter PKE of SIUL2 is set or not), but you did not disable it after wakeup, the SIUL2 module can not be initialized again.

This is tricky since our chip design enabled this padkeeping feature by default. If you don’t need the padkeeping function while the MCU needs to go to standby mode and wakeup, you need to write 1 to this bit anywhere and leave it alone.