- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144 LSPI

S32K144 LSPI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144 LSPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

i use the LPSPI_s32k144 example,i have a question.

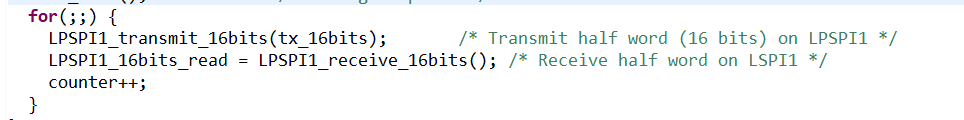

if do this is ok,no problem

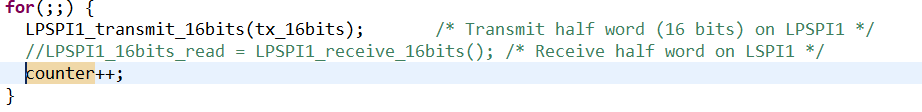

but if i do this

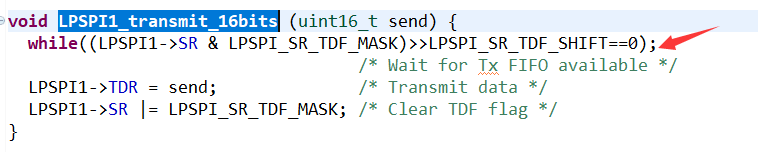

is inly send message ,not receive ,when counter=10,it will stop ,not run .

i only need send message,and not any slave send to me ,so my receive buff not

any message ,why it stop here?

and why the receive will affect the send

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

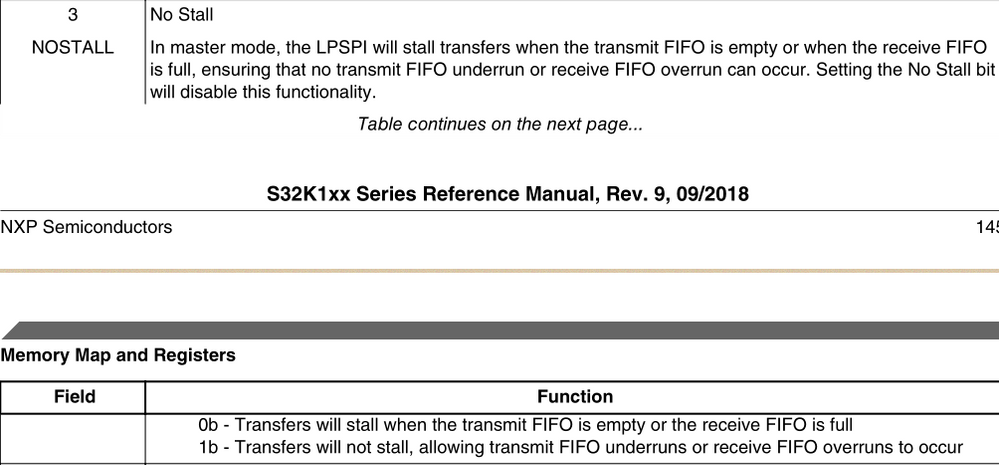

In this case, you need to set CFGR1_NOSTALL.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks reply ,

i look this ,and i already set LPSPI1->CFGR1 = 0x00000001;

LPSPI1->CR = 0x00000000; /* Disable module for configuration */

LPSPI1->IER = 0x00000000; /* Interrupts not used */

LPSPI1->DER = 0x00000000; /* DMA not used */

LPSPI1->CFGR0 = 0x00000000; /* Defaults: */

/* RDM0=0: rec'd data to FIFO as normal */

/* CIRFIFO=0; Circular FIFO is disabled */

/* HRSEL, HRPOL, HREN=0: Host request disabled */

LPSPI1->CFGR1 = 0x00000001; /* Configurations: master mode*/

/* PCSCFG=0: PCS[3:2] are enabled */

/* OUTCFG=0: Output data retains last value when CS negated */

/* PINCFG=0: SIN is input, SOUT is output */

/* MATCFG=0: Match disabled */

/* PCSPOL=0: PCS is active low */

/* NOSTALL=0: Stall if Tx FIFO empty or Rx FIFO full */

/* AUTOPCS=0: does not apply for master mode */

/* SAMPLE=0: input data sampled on SCK edge */

/* MASTER=1: Master mode */

LPSPI1->TCR = 0x5300000F; /* Transmit cmd: PCS3, 16 bits, prescale func'l clk by 4, etc*/

/* CPOL=0: SCK inactive state is low */

/* CPHA=1: Change data on SCK lead'g, capture on trail'g edge*/

/* PRESCALE=2: Functional clock divided by 2**2 = 4 */

/* PCS=3: Transfer using PCS3 */

/* LSBF=0: Data is transfered MSB first */

/* BYSW=0: Byte swap disabled */

/* CONT, CONTC=0: Continuous transfer disabled */

/* RXMSK=0: Normal transfer: rx data stored in rx FIFO */

/* TXMSK=0: Normal transfer: data loaded from tx FIFO */

/* WIDTH=0: Single bit transfer */

/* FRAMESZ=15: # bits in frame = 15+1=16 */

LPSPI1->CCR = 0x04090808; /* Clock dividers based on prescaled func'l clk of 100 nsec */

/* SCKPCS=4: SCK to PCS delay = 4+1 = 5 (500 nsec) */

/* PCSSCK=4: PCS to SCK delay = 9+1 = 10 (1 usec) */

/* DBT=8: Delay between Transfers = 8+2 = 10 (1 usec) */

/* SCKDIV=8: SCK divider =8+2 = 10 (1 usec: 1 MHz baud rate) */

LPSPI1->FCR = 0x00000003; /* RXWATER=0: Rx flags set when Rx FIFO >0 */

/* TXWATER=3: Tx flags set when Tx FIFO <= 3 */

LPSPI1->CR = 0x00000009; /* Enable module for operation */

/* DBGEN=1: module enabled in debug mode */

/* DOZEN=0: module enabled in Doze mode */

/* RST=0: Master logic not reset */

/* MEN=1: Module is enabled */

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I don't see the bit being set in the code.

It should be:

LPSPI1->CFGR1 = 0x00000009;

// [3] NOSTALL = 0b1

// [0] MASTER = 0b1

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi ,

yes ,is ny bad ,and i do LPSPI1->CFGR1 = 0x00000009; is OK

but i still have a problem ,not any salve send to me, why the receive buff have data?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The LPSPI module is always reading the MISO port even if the pin is disconnected.

The example that you were using stopped transmitting when the RX FIFO was full to prevent overflowing.

The NOSTALL bit allows transmitting even if the RX FIFO is full.

I mentioned that to point out the issue here was the RX FIFO overflow.

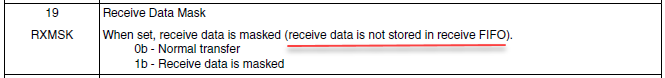

But you can mask the RX data TCR_RXMSK = 1.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

it really helps ,thank your very.

haiyang