- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144 ECC Fault Test

S32K144 ECC Fault Test

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K144 ECC Fault Test

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We want to enable ECC check on SRAM for our existing project on S32K144. I did go through the Datasheet and also this example link: Example S32K14x SRAM ECC Injection - NXP Community

1. The example code uses EIM to inject fault on read and validate the ECC function and hits the respective ISR's(ERM_single_fault_IRQHandler, ERM_double_fault_IRQHandler).

2. In my understanding, any read of variable without first writing to it should cause a double fault. So I didnt configure EIM and tried reading an uninitialized local and global variable, which didn't fault out.

My code (Stripped down version of example code above) -

- ERM Init

- Enable single and double fault interrupt.

- MCM Init and enable MCM IRQ.

- Read an uninitialized variable in anticipation of capturing the fault address through ISR.

This doesn't seem to be working for me. Appreciate your support in understanding what could be going wrong here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First I want to say that your understanding is correct.

According to: AN12522-S32K1xx ECC Error Handling.

2.1 SRAM initialization after power-on-reset

The reset state of the SRAM is unknown, thus data may contain random data. Most probably the first read attempt to any address would generate non-correctable ECC error. It is essential that each memory address be written to a known value before being read. If an uninitialized memory address is read, it is likely the read will result in a multiple-bit ECC error and an errored transaction on the AHB. Therefore, the SRAM must be initialized after power-up and this includes the peripherals RAM memories as the LPUART and FlexCAN RAMs.

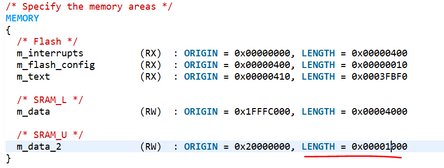

But you forgot that the SRAM has been initialized by default when power is on. So you need to modify the startup code to turn off the power-on initialization of the SRAM.

I tested this code on Keil and the result is the same as you expected.

BR!

Jim,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Senlent

Thanks for the quick response. Maybe I forgot to mention that I had already stripped the Init RAM ECC code from startup_S32K144.s file. For some reason, the memory address is zero filled on startup even for local variables.

I'm hereby attaching the project folder for reference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Senlent

Sorry for the late response. Though the memory address had stale data, reading from that location with ECC enabled didnt generate any fault.

Could there be something else we are missing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

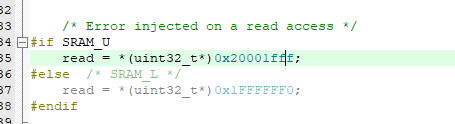

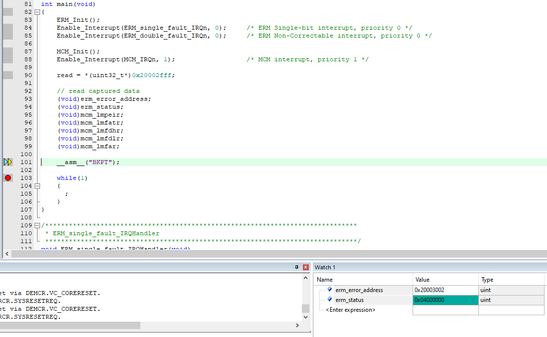

I made a test again,and it works fine on my side.(s32k142 & keil )

The appendix is the routine in the IDE, and I modified it according to your method, and the test result is normal.

I'm using S32K142EVB and RTM3.0 instead of S32K144,but I think it is the same.

BR!

Jim,