- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K144: Cache enable/disable question

S32K144: Cache enable/disable question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, all

I use the following statement for cache enable.

Q1: The following statement is ok? Does this statement can enable both instructions cache and data cache? And don't need other configuration for cache enable?

LMEM->PCCCR = LMEM_PCCCR_INVW0(1) | LMEM_PCCCR_INVW1(1) | LMEM_PCCCR_GO(1) | LMEM_PCCCR_ENCACHE(1);

when i want to disable PFLASH cache temporarily before modifying PFLASH,

Q2: The following statement is ok? And don't need to flush data(in cache) to destination before PFLASH cache disable? If needed, how to flush?

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM1(0x3u);

when i want to disable cache temporarily,

Q3: The following statement is ok? And don't need to flush data(in cache) to destination before cache disable? If needed, how to flush?

LMEM->PCCCR = LMEM_PCCCR_INVW0(1) | LMEM_PCCCR_INVW1(1) | LMEM_PCCCR_GO(1);

Regards,

Liu

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Liu,

Sorry for the misunderstood. I was confused by questions two and three, please see my comments below.

when i want to disable PFLASH cache temporarily before modifying PFLASH,

Q2: The following statement is ok? And don't need to flush data(in cache) to destination before PFLASH cache disable? If needed, how to flush?

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM1(0x3u);

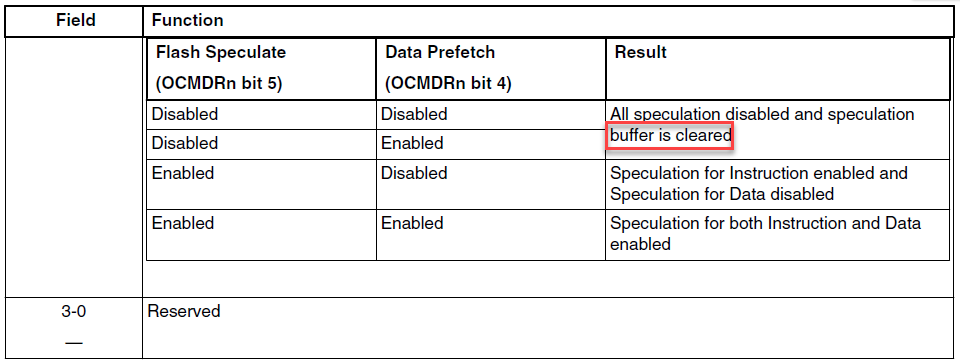

What you are deactivating here is the speculation buffer. When you deactivate this buffer it will be cleared automatically. You don't need to back up this information since it's already in the flash memory. However, since this is a read-only buffer, you don't need to deactivate it before modifying PFLASH.

when I want to disable cache temporarily,

Q3: The following statement is ok? And don't need to flush data(in cache) to destination before cache disable? If needed, how to flush?

LMEM->PCCCR = LMEM_PCCCR_INVW0(1) | LMEM_PCCCR_INVW1(1) | LMEM_PCCCR_GO(1);

As mentioned before, your statement is correct, but I recommend you to add the lines that I mentioned in my last reply.

Here you don't need to back-up the data. By default, the local memory controller is in write-through mode. A write-through write hit updates the cache hit data and writes to the output bus.

Regards,

Victor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Liu,

Regarding your questions please see my comments below.

Q1: The following statement is ok? Can this statement enable both instructions cache and data cache? And don't need other configuration for cache enable?

Your statement's correct, you only need that to enable the cache.

Q2: The following statement is ok? And don't need to flush data(in cache) to a destination before PFLASH cache disable? If needed, how to flush?

This statement is correct. Noticed that when you do this the buffer is cleared automatically.

Q3: The following statement is ok? And don't need to flush data(in cache) to a destination before cache disable? If needed, how to flush?

Your statement is correct. However, I recommend you to add the following statements.

/* Enables the processor code bus to invalidate all lines in both ways.

and Initiate the processor code bus code cache command. */

base->PCCCR |= LMEM_PCCCR_INVW0_MASK | LMEM_PCCCR_INVW1_MASK | LMEM_PCCCR_GO_MASK;

/* Wait until the cache command completes. */

while (base->PCCCR & LMEM_PCCCR_GO_MASK)

{

}

/* As a precaution clear the bits to avoid inadvertently re-running this command. */

base->PCCCR &= ~(LMEM_PCCCR_INVW0_MASK | LMEM_PCCCR_INVW1_MASK);

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

Thanks for your reply.

Regarding your answer marked with red on Q2, what is the mean of "buffer is cleared"?

It will execute 2 steps: 1. flush cache content to destination; 2. invalidate cache content

Is it right?

I am concerned about the valid content behavior in cache.

Regards,

Liu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Liu,

Sorry for the misunderstood. I was confused by questions two and three, please see my comments below.

when i want to disable PFLASH cache temporarily before modifying PFLASH,

Q2: The following statement is ok? And don't need to flush data(in cache) to destination before PFLASH cache disable? If needed, how to flush?

MSCM->OCMDR[0u] |= MSCM_OCMDR_OCM1(0x3u);

What you are deactivating here is the speculation buffer. When you deactivate this buffer it will be cleared automatically. You don't need to back up this information since it's already in the flash memory. However, since this is a read-only buffer, you don't need to deactivate it before modifying PFLASH.

when I want to disable cache temporarily,

Q3: The following statement is ok? And don't need to flush data(in cache) to destination before cache disable? If needed, how to flush?

LMEM->PCCCR = LMEM_PCCCR_INVW0(1) | LMEM_PCCCR_INVW1(1) | LMEM_PCCCR_GO(1);

As mentioned before, your statement is correct, but I recommend you to add the lines that I mentioned in my last reply.

Here you don't need to back-up the data. By default, the local memory controller is in write-through mode. A write-through write hit updates the cache hit data and writes to the output bus.

Regards,

Victor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor

In Q2 you replied : ...you don't need to deactivate it before modifying PFLASH.

But what about this scenario/problem described here?

https://community.nxp.com/message/880253?commentID=880253#comment-880253

thanks

best regards

Jochen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

Thanks for your information.

It's cleared to me for Q2.

For Q3.

Just as you said, the default setting about region is Write-through, and there is no need to back-up the data.

So, if i change the setting to Write-back mode, do i need to bake-up the data if i use your statements as you mentioned before?

If yes, How i bake-up the data under Write-back mode.

Thanks again!!!

Regards,

Liu.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Liu,

In write-back mode initially, writing is done only to the cache. The write to the backing store is postponed until the modified content is about to be replaced by another cache block. Unfortunately, there isn't a way to control this. If you want to eliminate the risk of data loss you must use write-through mode.

Regards,

Victor.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Victor,

Thanks for your reply.

It's a great pity that there is no way to flush cache data to backing store in write-back mode.

Because i think the performance in write-back mode is better than in write-through mode.

But it's clear to me for these modes, thanks again.

Have a nice day!

Regards,

Liu.