- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K ECC functionality

S32K ECC functionality

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are trying to understand which memory types of the S32K is protected by ECC. It is clear from the S32K1xx Series Reference Manual that both sections of RAM is protected as well as how to detect both single-bit and double-bit ECC errors. For the FlexNVM module it is also clear that if it is configured as Data Flash or Emulated EEPROM, single-bit ECC errors are automatically corrected and how to detect double-bit ECC errors. If CSEc is used, it is also clear that CSE_PRAM area is protected.

However, for the regular data/program flash (ex in S32K148 address range: 0000_0000-0017_FFFF ), it is not clear for us from the Reference Manual or other S32K documentation if it is ECC protected and how. It seems like double-bit faults in regular flash is reported in register FTFC->FERSTAT->DFDIF (Double Bit Fault Detect Interrupt Flag). Is this correct? For single-bit faults in regular flash there is less information: Is it in place for regular flash? Is it automatically corrected? Is there any reporting of it?

Best regards,

André

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's a good point, you are right. Sorry, I mismatched that with another devices where it is possible.

I just confirmed that there's no flag for single bit error. Only double bit error can be reported on flash.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have a few related questions on this topic:

1. Is there a way, either in software or hardware, to 'scrub' memory that needs ECC correction? ('scrubbing' means writing back the correct value to the memory location so it won't need ECC correction next time).

2. In case of double bit errors, how is this reported? Does the user application need to read the register mentioned in this discussion or is there some asynchronous (e.g. interrupt) method also exists?

Thanks for your help

Durga Choudhury

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

program and data flash is protected by ECC too.

Are you aware of this application note?

https://www.nxp.com/docs/en/application-note/AN12522.pdf

It should answer all your questions.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

After reading the application note, it is still a bit unclear to us about the single-bit fault for flash. Following information exist in the application note:

The ECC logic implemented in the S32K1xx Flash memory can correct single-bit fault automatically and can detect multiple-bit fault in each NVM sections. The multiple-bit fault is enabled using the FERCNFG[DFDIE] bit. When the multiple-bit error is detected, the FERSTAT[DFDIF] flag is set, and the interrupt request is generated.

- Since the formulation above is "can correct single-bit fault automatically", is there any action needed to turn on the correction?

- Is there any reporting of single-bit faults in flash?

Best regards,

André

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi André,

yes, single bit errors are automatically corrected. This feature can't be turned off.

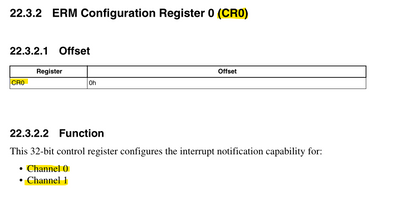

Reporting can be enabled in Error Reporting Module in CR0 register if needed.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Lukas,

Then our doubts regarding enabling of single bit error correction are clear, thank you!

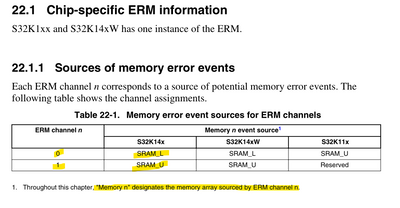

Regarding Error Reporting, the latest Reference Manual for S32K (Rev. 12.1, 02/2020) states that the mentioned register is used only for RAM error reporting. Is this not the case?

Best regards,

André

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That's a good point, you are right. Sorry, I mismatched that with another devices where it is possible.

I just confirmed that there's no flag for single bit error. Only double bit error can be reported on flash.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Lukas for your fast support in this matter!

Have a nice evening.

Best regards,

André

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the quick reply! We have not seen this specific application note, we will review it and hopefully it should clear out our doubts.

Best regards,

André