- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PWM_BCTU_ADC

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I am currently designing an ADC reading system where I trigger the BCTU using PWM flags in OPWMT mode. I have set up three triggers for the BCTU, each offset to ensure that signals are sampled sequentially and stored in the FIFO in the correct order. This way, I can be certain that the data in FIFO[0] corresponds to the first signal, FIFO[1] to the second signal, and FIFO[2] to the third signal.

The setup is as follows:

- PWM Trigger CH3 —> BCTU —> ADC 0

- PWM Trigger CH1 —> BCTU —> ADC 1

- PWM Trigger CH2 —> BCTU —> ADC 2

I have designed my ADC reading system as described, but the signals are not appearing in the correct order. Could you please assist me with this issue? I have attached my project.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi@Ayaz

I'm sorry, I'm dealing with your problem, but it will take me some time to figure out the reason, please be patient

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @Senlent ,

I would like to know the order of signals that is stored in the BCTU FIFO considering trigger offsets.

ADC0 signals are grouped together and a single trigger triggers it (no cross triggering). The same is done with ADC1 and ADC2.

Now, since I have offset the triggers, I would expect that the BCTU FIFO is filled in the order of the offset.

Consider the example that I sent you (all in OPWMT mode):

EMIOS_0_3 has an offset value of 1

EMIOS_0_1 has an offset of 312

EMIOS_0_2 has an offset of 416

Here is my BCTU configuration

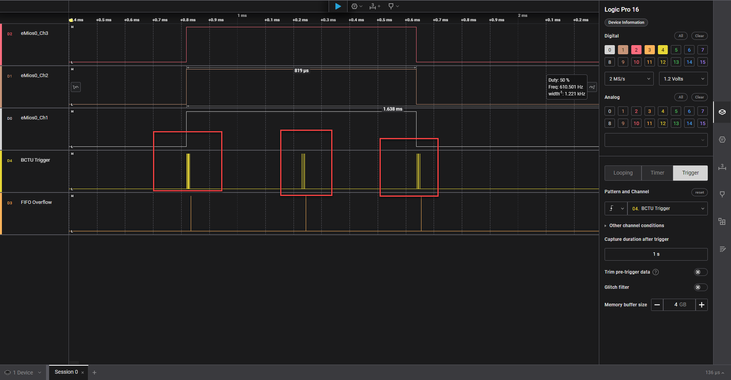

When I plotted the eMIOS trigger I can see the trigger offset on the oscilloscope.

Considering that the BCTU FIFO is empty at the start, I expect that the EMIOS_0_3 will be the first to generate a trigger to the BCTU. The signals ADC0_A_RD and ADC0_B_RD will be sampled first and will be filled in the BCTU FIFO[0] and BCTU FIFO[1].

The next trigger will be EMIOS_0_1 and will sample the signals ADC1_A and ADC1_B. These 2 values will be stored in the BCTU FIFO[2] and BCTU FIFO[3] respectively.

Finally the last trigger EMIOS_0_2 which will sample ADC2_A and ADC2_B and store it in BCTU FIFO[2] and BCTU FIFO[3] respectively.

But when I read the first 6 BCTU FIFO values using Bctu_Ip_GetFifoResult API I see the following order

This is not as per the expectation. Could you help me with what is going wrong?

P.S.: The sample time for all the ADC's are the same.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

With respect to your timing diagram, would the 'BCTU Trigger' be triggered every time the ADC is triggered by the BCTU (BCTU output trigger) or the eMIOS triggers the BCTU (BCTU input trigger)?

Also, if we have a MPC (cross trigger) where the 6 signals were triggered in the below way:

- signal 1 and signal 2 parallelly sampled

- signal 3 and signal 4 parallelly sampled

- signal 5 and signal 6 parallelly sampled

Would we still see the 'BCTU Trigger' triggered 6 times or 3?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi@Samuel_DCosta

Please ignore the previous answer

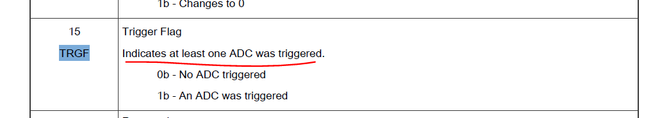

1.Would the 'BCTU Trigger' be triggered every time the ADC is triggered by the BCTU (BCTU output trigger) or the eMIOS triggers the BCTU (BCTU input trigger)?

According to the BCTU MCR->TRGF register,it should be the fisrt one which is BCTU output trigger to ADC.

2.Also, if we have a MPC (cross trigger) where the 6 signals were triggered in the below way:

- signal 1 and signal 2 parallelly sampled

- signal 3 and signal 4 parallelly sampled

- signal 5 and signal 6 parallelly sampled

Would we still see the 'BCTU Trigger' triggered 6 times or 3?

This is related to your BCTU configuration. You need to give me a specific configuration so that I can answer your question.

In short, there is no problem with your project and your's understanding is right.

I modified your demo and tested it.(Please refer to the attachments)

The incorrect data order in the FIFO may be caused by the following reasons.

You will find that this is because there are some problems in the first cycle of PWM, which leads to inconsistent FIFO storage order.

I modified the trigger points of OPWMT to Ch3, Ch1, Ch2, the watermask value is 3, and the sampling is 4 times each time the trigger is triggered, for a total of 12 samples.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

S32K344

RTD 5.0.0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

eMios0_Ch3->ADC0.Ch38

eMios0_Ch3->ADC0.Ch39

eMios0_Ch1->ADC1.Ch6

eMios0_Ch1->ADC1.Ch7

eMios0_Ch2->ADC2_Ch4

eMios0_Ch2->ADC2_Ch3

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Offset in ticks = core clock * time (us) . But the trigger start from 1 .

My question is is the the formula above should be +1 or -1 ??