- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: NXP s32k312 SRAM MultibitError

NXP s32k312 SRAM MultibitError

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NXP s32k312 SRAM MultibitError

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m able to hit the SRAM ISR (ERM0_ISR_Handler) for single-bit errors, but the handler is not being called for multi-bit errors.

As far as I understand, a non-correctable error event corresponds to a multi-bit error, correct?

I can see that the SRAM non-correctable error event bit is set in SR0, but the ISR is not being triggered.

Could you please help me understand how to call the multi-bit error ISR?

I enabled interrupt notification for SRAM0 in CR0 register also

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Anitha7,

I updated the example by adding uncorrectable error injection into SRAM0.

Can you read the VTOR register in your application?

The interrupt vector table must not reside in SRAM0 when injecting an uncorrectable ECC fault into the memory.

Otherwise, the ECC fault would corrupt the vector table during a fetch leading to another fault exception.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

VTOR table points to flash memory only during SRAM0 inject uncorrectable ECC fault.

I configured the system for an SRAM0 as per your reference example code. uncorrectable ECC fault occur by setting the corresponding bit in the SRO register.

I enabled interrupt notification in corresponding CR0 register.

After uncorrectable ECC fault occurs, control transfers to the system call function, software not working after that until i perform reset. The ERM_1_Handler is not being triggered, even though I have added it. For single-bit errors, the ERM_0_Handler is triggered correctly.

What should I do to ensure that the ERM_1_Handler is invoked when a multi-bit (uncorrectable) ECC error occurs?

Also, just to confirm — does a multi-bit error always indicate an uncorrectable ECC fault?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Anitha7,

What do you mean by a multi-bit error?

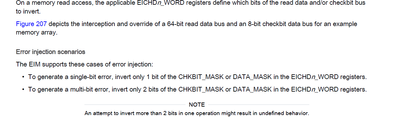

There is one 8-bit checksum for 64bits (8 bytes) of data, it is not possible to detect every posilble ECC error. There is ECC SECDED (Single error correction, Double error detection).

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Multibit means Double bit as per RM

I configured the system for an SRAM0 as per your reference. uncorrectable ECC fault occur(NEC0) by setting the corresponding bit in the SRO register.

I enabled interrupt notification for NEC0 and single bit event in corresponding CR0 register.

After Non correctable ECC fault occurs, control transfers to the system call function, software not working after that until i perform reset. The ERM_1_Handler is not being triggered, even though I have added it. For single-bit errors, the ERM_0_Handler is triggered correctly.

What should I do to ensure that the ERM_1_Handler is invoked when a multi-bit (uncorrectable) ECC error occurs?

Also, just to confirm — does a multi-bit error(double bit error) always indicate an uncorrectable ECC fault?

After Non correctable ECC event occurs i need to perform reset run in ECU in normal mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Anitha7,

Uncorrectable faults trigger a CM7 fault exception.

In the example I linked, I enabled the Bus_Fault exception, but with a lower priority than the priority of the ERM handler so that the ERM handler is called first.

I believe this might be the issue in your project.

Also, double-check the VTOR pointer and ensure that the ERM interrupt is enabled in the NVIC. You may notice the interrupt pending in NVIC.