- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Maximum SPI frequency in VLPS?

Maximum SPI frequency in VLPS?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have my S32K148 configured as a SPI slave, and am using VLPS mode with DMA wake-up after a SPI transfer completes (after which, it stays in run until it receives an explicit command over SPI to go back to VLPS). I'm expecting that I need to reduce the SPI clock frequency (generated by the master) while in VLPS, but in testing I'm finding that transfers succeed at full speed (SPI data clock at 12mhz) in VLPS. Why? Am I doing something wrong? Is this an indication I'm not successfully entering VLPS? Does the DMA wake-up enable the full-speed clock fast enough to allow the transfer to succeed? At what point in the SPI transfer does the DMA wake-up begin?

More details:

In normal run mode I'm clocking the SPI peripheral at 48mhz through FIRC, and the SPI master generates a 12mhz data clock. In VLPS, I set the SPI peripheral clock source to SIRCDIV2, which is SIRC/2 (4mhz) so I expect I can run SPI transfers at 2mhz.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nathan,

I'm sorry for the delay.

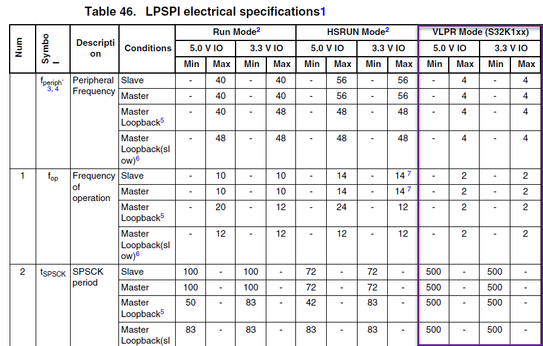

The LPSPI VLPR specification applies to VLPS as well.

We can't guarantee proper functionality of the module at higher bit rates.

S32K1xx Datasheet, rev.13

DMA wake-up operation is explained in details in the RM, rev12.1 Section 39.4.3.

You can verify the MCU is in VLPS by measuring the VDD consumption and BUS_CLK on an CLKOUT pin.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. I'm not sure what I'd been doing wrong, but I now have more of my system working, and found that I do need to reduce the SPI data clock frequency when the MCU is in VLPS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nathan,

I'm sorry for the delay.

The LPSPI VLPR specification applies to VLPS as well.

We can't guarantee proper functionality of the module at higher bit rates.

S32K1xx Datasheet, rev.13

DMA wake-up operation is explained in details in the RM, rev12.1 Section 39.4.3.

You can verify the MCU is in VLPS by measuring the VDD consumption and BUS_CLK on an CLKOUT pin.

Regards,

Daniel