- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: LPUART LIN baudrate deviation issue

LPUART LIN baudrate deviation issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPUART LIN baudrate deviation issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am using LPUART1 as an instance for using s32k sdk LIN STACK with baud rate = 19200bps and Im having the following issue:

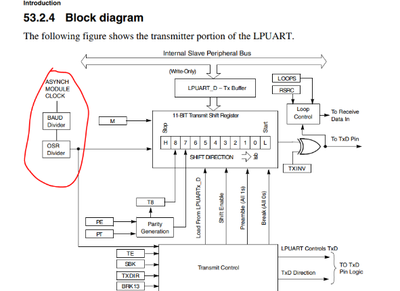

The LPUART module seems to have 2 different divisors for the input clock configured for this peripheral:

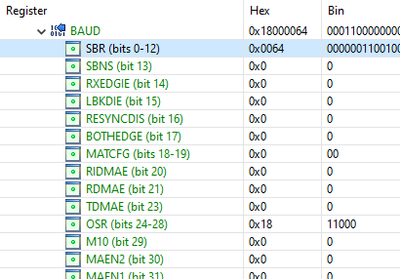

The BAUD divider (sbr), which is just a modulo divide rate, and the OSR divider (osr), which is an oversampling ratio for the baud rate generated.

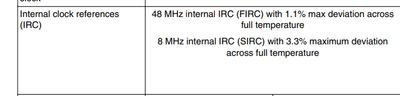

I´m trying to improve the accuracy of the baud rate generated for the LIN communication, so i´m trying different clock configurations, because reference manual says that FIRC and SIRC clock have different deviation accross temperature:

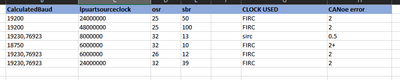

Following this image, i was expecting that using FIRC clock with this peripheral, the baud rate accuracy will improve, but my results are showing the following:

Notes:

(CalculatedBaud = lpuartSourceClock / (osr*sbr)

CANoe error = baud rate deviation reported by CANoe in percentage of 100 (%)

The best accuracy i could achieve, is 0.5% deviation respect LIN master baud rate, using SIRC and 8Mhz for the clock, but in the other configurations with the FIRC, which is suppossed to be more precise, i could only achieve 2% of desviation.

I reviewed the osr and sbr parameters calculated by the NXP lin stack and they seem to be OK, so at this point i dont understand why the baud rate generated is not that good as the obtained with the SIRC...

Hope the explanation is clear enough and thank you for the help

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @riglesias2021 ,

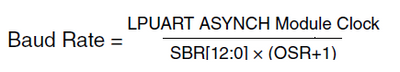

I haven't calculated it yet, however, the equestion that you use is not correct:

Can you double-check?

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thats the same formula i used, the difference is the NXP Lin stack decrements the OSR before setting it to the LPUART registers, so the result is the same

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @riglesias2021,

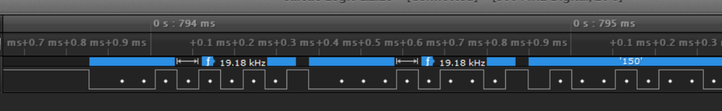

I just tested it with the S32K118 EVB and lpuart_echo_s32k118 (RTM 4.0.2) example.

Only changes:

- PTC3 as TX

- FIRC_DIV2 48MHz LPUART functional clock

- SBR 0x64 = 100, OSR = 0x18 = 24

And the TX signal looks correct:

Can you please scope the following:

- TX signal

- LIN signal

- FIRCDIV2 at CLKOUT

Thanks,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, thank you for the reply.

From my side it seems that the FIRC precission was corrected after enabling the "FIRC Regulator". I cant find too much information about this regulator in the s32k118 reference manual, but it seems that this feature improves the clock deviation so my issue was corrected after enabling this feature.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @riglesias2021,

Thanks for the updated.

This seems to be correct.

Answer from the design team:

"The FIRCREGOFF bit is used to control an internal regulator used by the FIRC internal circuit. In order to guarantee the operation frequency of the FIRC, the application must make sure to set this bit. Otherwise, FIRC operational frequency may get out of spec."

Regards,

Daniel