- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

LPSPI 8 32bit words in one frame S32K142

Need to configure S32K142 LPSPI to talk to NXP NJJ29C2 LF driver chip 8 32bit words in one frame.

Hello I need to configure S32K142 LPSPI to talk to NXP NJJ29C2 LF driver.

It requires a SPI single frame with 256 bits i.e. 8 32bit words..

I have attempted to configure the LPSPI on our S32K142 as shown below... and it does not work.

It starts transmission and does have a neg going CS and sends out 6 32bit words nad then does not send anymore.

It does finish the for loop in the TX shown below, i.e. it is not hung waiting for the LPSPI_SR_TDF_MASK, it simply does not send any more data after the 6th 32bit word, also no sclk after the 6th 32bit word, and CS is and stays asserted low forever.

Please advise on how you are using S32K142 to talk to NJJ29C2, and or example code, and or fixes to my configuration etc.

After we get through the data sending I will need to know how to receive the 8 32bit words from the NJJ29C2

The LSSPI setup ---

void LPSPI1_init_master(void)

{

PCC->PCCn[PCC_LPSPI1_INDEX] = 0; /* Disable clocks to modify PCS ( default) */

PCC->PCCn[PCC_LPSPI1_INDEX] = 0xC6000000; /* Enable PCS=SPLL_DIV2 (40 MHz func'l clock) */

LPSPI1->CR = 0x00000000; /* Disable module for configuration */

LPSPI1->IER = 0x00000000; /* Interrupts not used */

LPSPI1->DER = 0x00000000; /* DMA not used */

LPSPI1->CFGR0 = 0x00000000; /* Defaults: */

/* RDM0=0: rec'd data to FIFO as normal */

/* CIRFIFO=0; Circular FIFO is disabled */

/* HRSEL, HRPOL, HREN=0: Host request disabled */

LPSPI1->CFGR1 = 0x00000001; /* Configurations: master mode*/

/* PCSCFG=0: PCS[3:2] are enabled */

/* OUTCFG=0: Output data retains last value when CS negated */

/* PINCFG=0: SIN is input, SOUT is output */

/* MATCFG=0: Match disabled */

/* PCSPOL=0: PCS is active low */

/* NOSTALL=0: Stall if Tx FIFO empty or Rx FIFO full */

/* AUTOPCS=0: does not apply for master mode */

/* SAMPLE=0: input data sampled on SCK edge */

/* MASTER=1: Master mode */

LPSPI1->TCR = 0x800000FF; // for 256 bits in one frame i.e. 8 32bit words

/* CPOL=1: SCK inactive state is high */

/* CPHA=0: Data is captured on the leading edge of SCK and changed on the following edge of SCK*/

/* PRESCALE=2: Functional clock divided by 2**2 = 4 */

/* PCS=0: Transfer using PCS0 */

/* LSBF=0: Data is transferred MSB first */

/* BYSW=0: Byte swap disabled */

/* CONT, CONTC=0: Continuous transfer disabled */

/* RXMSK=0: Normal transfer: rx data stored in rx FIFO */

/* TXMSK=0: Normal transfer: data loaded from tx FIFO */

/* WIDTH=0: Single bit transfer */

/* FRAMESZ=256: # bits in frame = 255+1=256 */

LPSPI1->CCR = 0x04090808; /* Clk dividers based on prescaled func'l clk of 100 nsec */

/* SCKPCS=4: SCK to PCS delay = 4+1 = 5 (500 nsec) */

/* PCSSCK=4: PCS to SCK delay = 9+1 = 10 (1 usec) */

/* DBT=8: Delay between Transfers = 8+2 = 10 (1 usec) */

/* SCKDIV=8: SCK divider =8+2 = 10 (1 usec: 1 MHz baud rate) */

LPSPI1->FCR = 0x00000003; /* RXWATER=0: Rx flags set when Rx FIFO >0 */

/* TXWATER=3: Tx flags set when Tx FIFO <= 3 */

LPSPI1->CR = 0x00000009; /* Enable module for operation */

/* DBGEN=1: module enabled in debug mode */

/* DOZEN=0: module enabled in Doze mode */

/* RST=0: Master logic not reset */

/* MEN=1: Module is enabled */

}

//----------------------------------------------------------------------------

// the TX

for(i= 0; i < 8; i++)

{

send = xmit_array[i];

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

/* Wait for Tx FIFO available */

LPSPI1->TDR = send; /* Transmit data */

LPSPI1->SR |= LPSPI_SR_TDF_MASK; /* Clear TDF flag */

}

Thank You

Brian

Hi Brian,

When the receive FIFO is not read, the LPSPI module stalls the transfer when the RX FIFO is full (FSR_RXCOUNT = 4).

You can either set the CFGR1_NOSTALL bit to avoid the stalling of the transfer or read the RX FIFO.

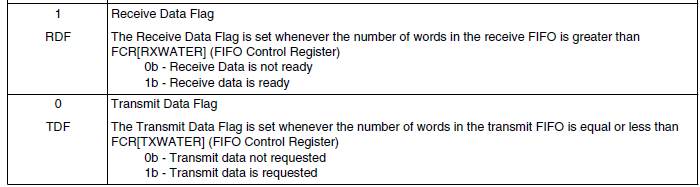

Please note that the SR[TDF, RDF] flags cannot be cleared by writing 1 to them.

They reflect the state of the FIFOs, to clear RDF, the RX FIFO needs to be read.

Regards,

Daniel

Hello Daniel:

OK I have added the RX

while((LPSPI1->SR & LPSPI_SR_RDF_MASK)>>LPSPI_SR_RDF_SHIFT==0); //<<---------------------- ONLY for 1 32 bit word received?

/* Wait at least one RxFIFO entry */

receive= LPSPI1->RDR; /* Read received data */

LPSPI1->SR |= LPSPI_SR_RDF_MASK; /* Clear RDF flag */

return receive; /* Return received data */

With the above it only receives one 32 bit word out of the 8 I should receive... I.E. the SR_RDF is never set again after the first received 32 bit word.

-------------------------------

The note on "the SR[TDF, RDF] flags cannot be cleared by writing 1 to them" that line of code for both transmit and receive comes directly

from the AN5413 "S32K1xx Series Cookbook example SPI as in

void LPSPI1_transmit_16bits (uint16_t send) {

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

/* Wait for Tx FIFO available */

LPSPI1->TDR = send; /* Transmit data */

LPSPI1->SR |= LPSPI_SR_TDF_MASK; /* Clear TDF flag */ //<<---------------------- from AN5413 Cookbook

}

uint16_t LPSPI1_receive_16bits (void) {

uint16_t receive = 0;

while((LPSPI1->SR & LPSPI_SR_RDF_MASK)>>LPSPI_SR_RDF_SHIFT==0);

/* Wait at least one RxFIFO entry */

receive= LPSPI1->RDR; /* Read received data */

LPSPI1->SR |= LPSPI_SR_RDF_MASK; /* Clear RDF flag */ //<<--------------------- from AN5413 Cookbook

return receive; /* Return received data */

}

Please explain... ??

-------------------------------

Also I am using "default" PARAM TXFIFO and RXFIFO should these be changed ??

Is my LPSPI1->FCR = 0x00000003; correct ?

Are all the other LPSPI1 registers (see original post) set correctly for 256 bit i.e. 8--- 32 bit words in one frame ?

etc.

Thank You

Brian

i Brian,

The example is clearly wrong.

The LPSPI_SR[RDF, TDF] flags are read-only unlike the other flags in the register.

And the flags simply reflects the state of the FIFOs which are configurable by FCR[RXWATER, TXWATER].

The PARAM register is also a read-only register. It specifies the maximum number of words in the FIFOs (4 words).

I don't see any issue in the configuration.

Could you attach your test code?

Thanks,

BR, Daniel

Hello Daniel:

<Could you attach your test code?>

See below.

If you needed this as a file I do not know how to attache on this forum etc.

Thanks

Brian

void LPSPI1_init_master(void)

{

PCC->PCCn[PCC_LPSPI1_INDEX] = 0; /* Disable clocks to modify PCS ( default) */

PCC->PCCn[PCC_LPSPI1_INDEX] = 0xC6000000; /* Enable PCS=SPLL_DIV2 (40 MHz func'l clock) */

LPSPI1->CR = 0x00000000; /* Disable module for configuration */

LPSPI1->IER = 0x00000000; /* Interrupts not used */

LPSPI1->DER = 0x00000000; /* DMA not used */

LPSPI1->CFGR0 = 0x00000000; /* Defaults: */

/* RDM0=0: rec'd data to FIFO as normal */

/* CIRFIFO=0; Circular FIFO is disabled */

/* HRSEL, HRPOL, HREN=0: Host request disabled */

LPSPI1->CFGR1 = 0x00000001;/* Configurations: master mode*/

/* PCSCFG=0: PCS[3:2] are enabled */

/* OUTCFG=0: Output data retains last value when CS negated */

/* PINCFG=0: SIN is input, SOUT is output */

/* MATCFG=0: Match disabled */

/* PCSPOL=0: PCS is active low */

/* NOSTALL=0: Stall if Tx FIFO empty or Rx FIFO full */

/* AUTOPCS=0: does not apply for master mode */

/* SAMPLE=0: input data sampled on SCK edge */

/* MASTER=1: Master mode */

LPSPI1->TCR = 0x800000FF; // for 256 bit

/* CPOL=0: SCK inactive state is low */

/* CPHA=1: Change data on SCK lead'g, capture on trail'g edge*/

/* PRESCALE=2: Functional clock divided by 2**2 = 4 */

/* PCS=0: Transfer using PCS0 */

/* LSBF=0: Data is transferred MSB first */

/* BYSW=0: Byte swap disabled */

/* CONT, CONTC=0: Continuous transfer disabled */

/* RXMSK=0: Normal transfer: rx data stored in rx FIFO */

/* TXMSK=0: Normal transfer: data loaded from tx FIFO */

/* WIDTH=0: Single bit transfer */

/* FRAMESZ=256: # bits in frame = 255+1=256 */

LPSPI1->CCR = 0x04090808; /* Clk dividers based on prescaled func'l clk of 100 nsec */

/* SCKPCS=4: SCK to PCS delay = 4+1 = 5 (500 nsec) */

/* PCSSCK=4: PCS to SCK delay = 9+1 = 10 (1 usec) */

/* DBT=8: Delay between Transfers = 8+2 = 10 (1 usec) */

/* SCKDIV=8: SCK divider =8+2 = 10 (1 usec: 1 MHz baud rate) */

LPSPI1->FCR = 0x00000003; /* RXWATER=0: Rx flags set when Rx FIFO >0 */

/* TXWATER=3: Tx flags set when Tx FIFO <= 3 */

LPSPI1->CR = 0x00000009; /* Enable module for operation */

/* DBGEN=1: module enabled in debug mode */

/* DOZEN=0: module enabled in Doze mode */

/* RST=0: Master logic not reset */

/* MEN=1: Module is enabled */

}

//----------------------------------------------------------------------------

//----------------------------------------------------------------------------

void LPSPI1_transmit_recieve_array(void)

{

uint8_t i

uint32_t send;

uint32_t receive;

#define XMIT_REC_ARRAY_SIZE 8

uint32_t xmit_array[XMIT_REC_ARRAY_SIZE];

uint32_t rec_array[XMIT_REC_ARRAY_SIZE];

for(i= 0; i < XMIT_REC_ARRAY_SIZE; i++)

{

send = xmit_array[i];

while((LPSPI1->SR & LPSPI_SR_TDF_MASK)>>LPSPI_SR_TDF_SHIFT==0);

/* Wait for Tx FIFO available */

LPSPI1->TDR = send; /* Transmit data */

//LPSPI1->SR |= LPSPI_SR_TDF_MASK; /* Clear TDF flag */ // <<---------------- per Daniel Martynek dont do this see thread in e-mail

// TODO: find out why not working

// Wait at least one RxFIFO entry

//while((LPSPI1->SR & LPSPI_SR_RDF_MASK)>>LPSPI_SR_RDF_SHIFT==0); // ???? if this is in place only recieave 1 32 bit word and we hang after that

// Wait at least one RxFIFO entry

receive = LPSPI1->RDR; // Read received data

//LPSPI1->SR |= LPSPI_SR_RDF_MASK; // Clear RDF flag // <<---------------- per Daniel Martynek dont do this see thread in e-mail

rec_array[i];

}

//----------------------------------------------------------------------------

Hello Brian,

There are many ways to implement it, you could use interrupts of DMA.

I modified the LPSPI example from the S32DS as simply as possible.

Please see the attached test project.

It is simply reading the TDF, RDF flags until all the data are placed in the TXFIFO and read from the RXFIFO.

You could also read the FSR[TXCOUNT, RXCOUNT] bit fields to see how many words there are in the FIFOs.

BR, Daniel