- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

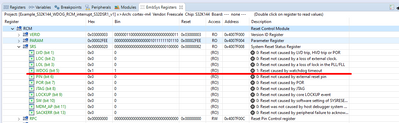

How to Read value of RCM_SRS?

Hello there:

Currently I ran into a problem that I don't know how to read the reasons of reset on S32K144. Before post this question, I have read the manual of "Chapter 26 Reset Control Module (RCM)". But I can't find the examples of RCM in SD2.0(there are adc,RTC,PWM,FTM and so on), and I haven't find when will MCU clean the values of RCM register. So I am finding help here to get some examples about RCM.

My question or needing list:

1.examples of RCM particularly about reading SRS;

2. when will MCU clean the values of RCM register, if I have to clean it by myself could you send some examples?

Thanks in advance!

Yes, it helps a lot and thank you very much!

But here I still have some questions:

1.before I read data from the SRS register, I have to set SRIE register first, and SRIE will reset after POR, so I need to set SRIE register every time at MCU init period, right?

2.after I get the value from SRS register, I am wondering when will the value in SRS register reset? Is that depending on the DELAY[bit0-bit1] Bit in SRIE register(In the example project both bit0 and Bit1 are 1, so it is 514 LPO cycles)? Or I need to clean the value in SRS from SSRS register by w1c?

Looking forward for your reply, Thanks!

Hello,

There is no need to set the SRIE bits.

This is needed only if you want to use the RCM interrupt to delay the reset.

As Diana mentioned, the SRS register is a read-only register.

You can refer to this example:

https://community.nxp.com/t5/S32K-Knowledge-Base/Example-S32K116-WDOG-Fast-Test/ta-p/1103420

The SRS register is read in startup_S32K116.c file (test_WDOG() function).

Unlike the SRS register status bits, the SSRS flags can be cleared.

Regards,

Daniel

Hello,

There is Example S32K144 WDOG RCM interrupt:

https://community.nxp.com/t5/S32K-Knowledge-Base/Example-S32K144-WDOG-RCM-interrupt/ta-p/1107039

The SRS is read-only. "The reset state of these bits depends on what caused the MCU to reset." When you use this example you can see that the reset is caused by WDOG.

I hope it helps.

Diana