- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

How do I setup continious PDB-ADC sampling

Hello,

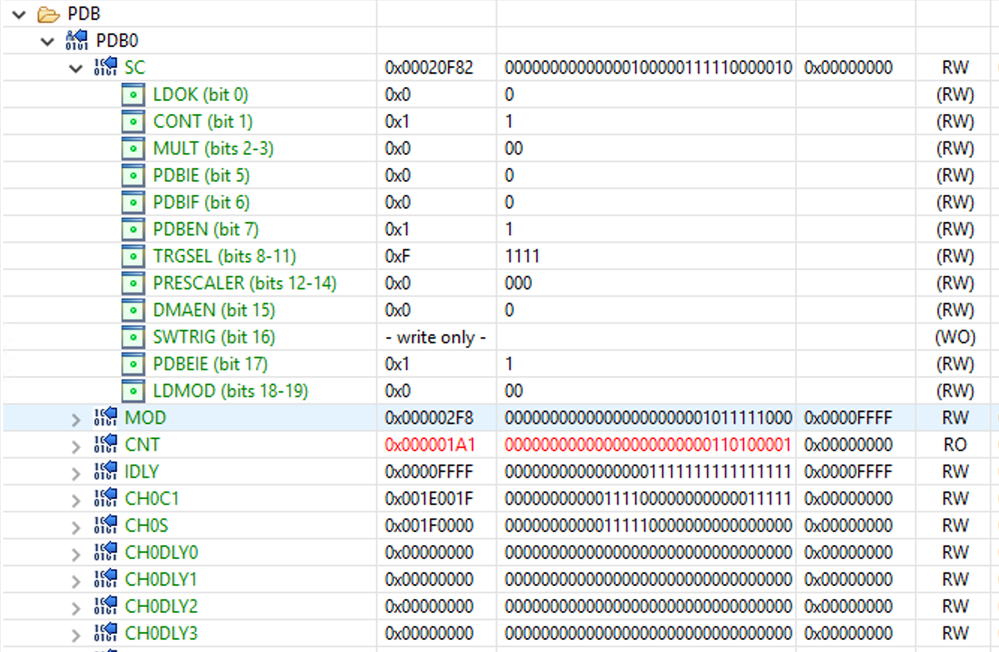

I try to setup PDB0-ADC0 for continious sampling. Below I have attached the register setup. PDB0 and ADC are clocked with 50 MHz. I am using a S32k144.

When I init the registers I see 1 sample only. I observe that the PDB counter count up until MOD and restarts at 0.

My expectation is that at restart this triggers new sampling. Also CH0S does not show any error.

What do I miss to do? Anything special to start continious sampling or do I setup the registers not correct?

Thanks in advance for your help or hint.

Edgar

Hello Edgar,

You are bypassing the delay registers.

Try setting the PDB_CHnC1_TOS bits.

Regards,

Daniel

Hello Daniel,

Thanks for your reply

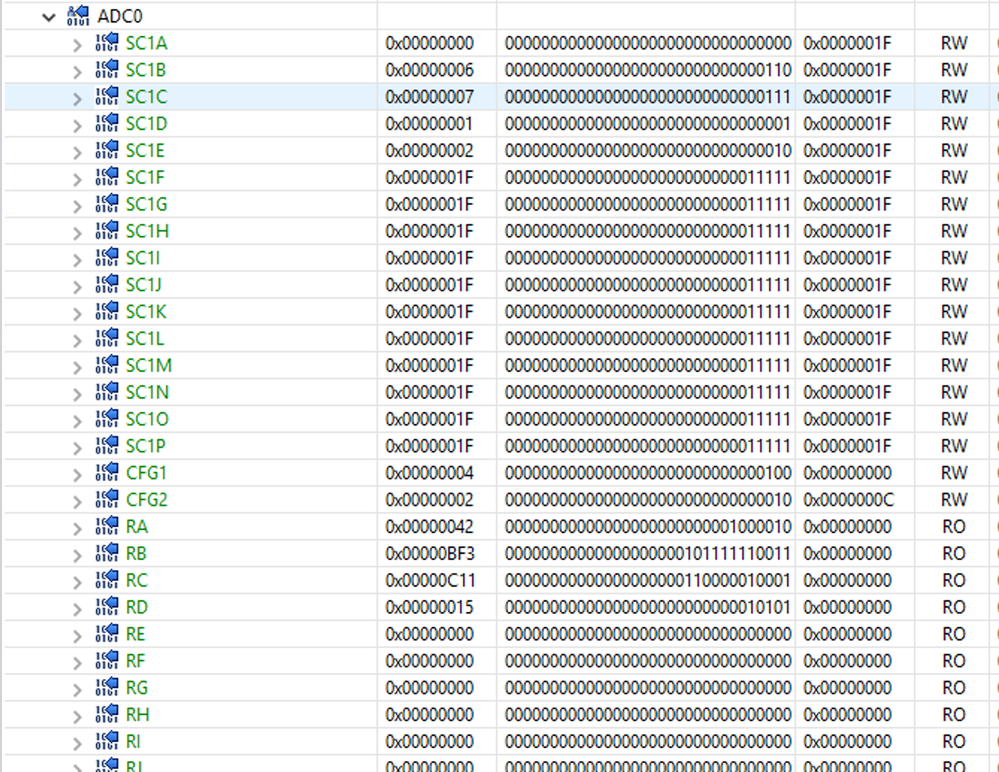

I tried this also. If I set the TOS bit and a delay eg 100 then the CF ist set after the COunter CNT reaches the delay

This screen below. I have tried several settings - with and w/o sw trigger. Also no BB but TOS Bits set and delay.

It is not clear to me how do I set properly continous mode. Setting TOS and delay register is of course also fin.

Basically what I need is a setup of the registers to sample 5 ADC channels continously at a maximum of 10 usec per loop.

Any idea or example how to set this up?

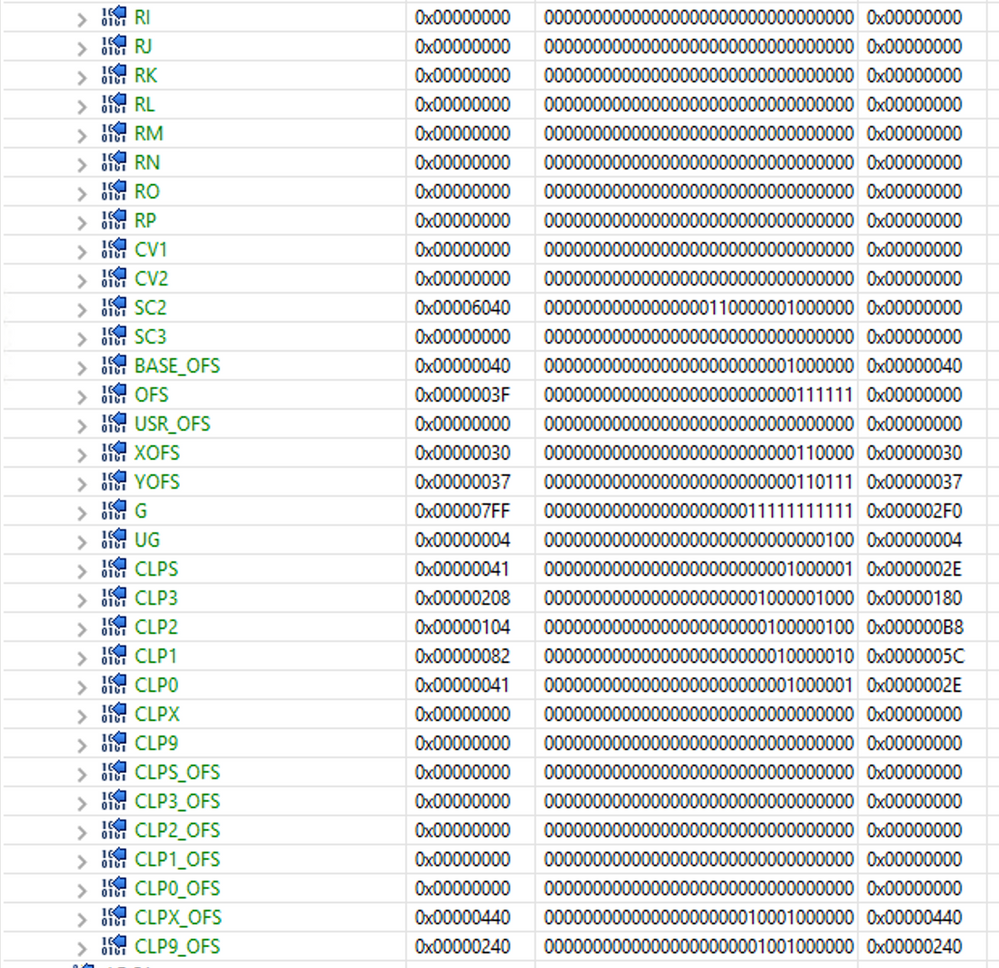

Maybe I shall mention that the ADC values not read after each conversion ie COCO is still set when the next conversion starts.

While debugging I guess that the CHOS-ERR are set for the channels if COCO is still set ie ADC value not read.

Is that the issue?

Hello Edgar,

Thank you for the additional information.

There are several ways to do it.

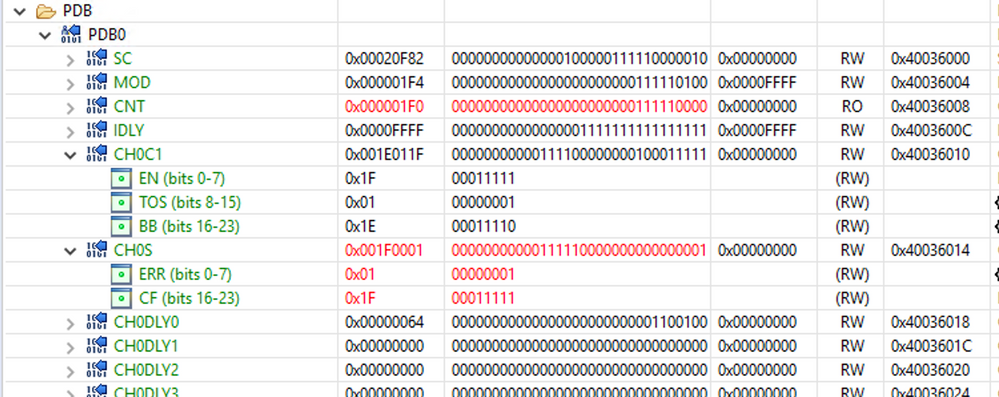

You can use either the Back-to-back One-Shot mode as shown in the below examples and then trigger the PDB back-to-back mode again with a SW trigger.

Example S32K144 PDB ADC back-to-back test S32DS12

Example S32K144 PDB ADC trigger DMA ISR S32DS

Or use the Back-to-back Continues mode.

For example: Initial SW trigger, first ADC conversion triggered by DLY[0], then back-to-back.

However, you need to read all the ADC result register to clear the COCO flags before the PDB back-to-back operation gets triggered again, before it reaches MOD.

void PDB_Init(void)

{

PCC->PCCn[PCC_PDB0_INDEX] |= PCC_PCCn_CGC_MASK; /* Enable bus clock in PDB0 */

PDB0->SC |= PDB_SC_TRGSEL(0xF) | /* b1111: Software trigger is selected */

PDB_SC_PDBEN_MASK; /* 1: PDB enabled */

PDB0->CH[0].C1 |= PDB_C1_BB(0x1E) | PDB_C1_TOS(0xFF) | PDB_C1_EN(0x1F);

// DLY[0] : pre-trigger from PDB DLY

// DLY[5:1] : back-to-back enabled

// Pretrigger Output Select: 0=bypassed , 1=enabled

// PDB channel's pre-trigger enabled

PDB0->MOD = FFFF; /* Specifies the period of the counter */

PDB0->CH[0].DLY[0] = 1; /* Pretrigger 0 */

PDB0->SC |= PDB_SC_LDOK_MASK;

}Also, you can use the PDB interrupt (configured by PDB_IDLY < MOD) and read the ADC results.

Or you could use the delay registers for all ADC channels.

Regards,

Daniel

Hello Daniel,

thanks for the help. It works now. In case someboday else has the same issue let me summerize what needs to be considered - the manual is very fuzzy in that area.

For continious sampling one shall use PDB. Even the sampling results are not needed immediately one must use DMA to handle COCO reset. Ie setup of DMA to a result buffer is necessary. It is best to use the BB feature however the first ADC channel must be triggered by the PDB counter ie for the first channel TOS must be enable with a delay of 1.

Also Software Trigger must be enabled. To start continious sampling PDB0 must be started by software

The PDB runs with system clock, ADC with bus clock . This must be considered to calculate the correct MOD value for PDB. For integration observer seqeunce error. It may be good to set MOD to 0xffff for first integration as in the example above.

Do not enable DMA interrupt in that case as you will receive an interrupt for every ADC sample.

Thanks again

Regards Edgar