- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

GPIO digital filter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm trying to configure in a S32K146 the digital filter function for the input pins, but I can not see any result. Is there more information about this function than the included in the Reference Manual?

Thank you,

Eduard.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

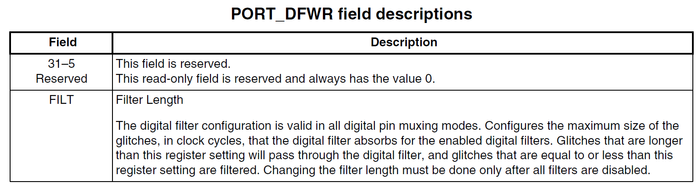

Is there (more) detailed information about how the filter works internally / which kind of filter is used?

E.g. the sentence "Configures the maximum size of the glitches, in clock cycles, that the digital filter absorbs for the enabled digital filters" regarding DFWR in the Reference Manual is not very illustrative (at least not to me).

What exactly are "glitches" in this case and how are they "absorbed" by the filter?

Thank you in advance!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @muellermathias,

It is just a simple digital filter.

Let's say there is a stable logic HIGH at the input.

If the digital filter is anabled, the Filter Length defines how long the input signal must be driven LOW before the MCU detects the falling edge.

Pulses that are shorter are absorbed.

I need to mention that the accuracy of the filter depends on the accuracy of the clock selected for the filter.

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Did you follow the configuration sequence in Section 12.1.3, RM r.8?

Can you share your code?

Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I followed the configuration sequence from section 11.1.3 (Digital input filter configuration sequence).

First of all I configured the pins through the function PINS_DRV_Init, then I write direct to the registers as follow:

PINS_DRV_Init(NUM_OF_CONFIGURED_PINS, g_pin_mux_InitConfigArr);

PORTB->DFCR = PORT_DFCR_CS(PORT_DIGITAL_FILTER_LPO_CLOCK);

PORTB->DFWR = PORT_DFWR_FILT(0x1F);

PORTB->DFER |= 1<<23;

PORTB->PCR[23] &= ~0x700;

PORTB->PCR[23] |= 0x100;

DelayFilter=0; while(DelayFilter<TIME_DELAY_FILTER) DelayFilter++;

PORTB->PCR[23] &= ~0x700;

PORTB->PCR[23] |= 0x100;

PORTC->DFCR = PORT_DFCR_CS(PORT_DIGITAL_FILTER_LPO_CLOCK);

PORTC->DFWR = PORT_DFWR_FILT(0x1F);

PORTC->DFER |= 1<<14;

PORTC->PCR[14] &= ~0x700;

PORTC->PCR[14] |= 0x100;

DelayFilter=0; while(DelayFilter<TIME_DELAY_FILTER) DelayFilter++;

PORTC->PCR[14] &= ~0x700;

PORTC->PCR[14] |= 0x100;

PORTC->DFCR = PORT_DFCR_CS(PORT_DIGITAL_FILTER_LPO_CLOCK);

PORTC->DFWR = PORT_DFWR_FILT(0x1F);

PORTC->DFER |= 1<<15;

PORTC->PCR[15] &= ~0x700;

PORTC->PCR[15] |= 0x100;

DelayFilter=0; while(DelayFilter<TIME_DELAY_FILTER) DelayFilter++;

PORTC->PCR[15] &= ~0x700;

PORTC->PCR[15] |= 0x100;

Regards,

Eduard.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Eduard,

Can you use the below code?

It does filter glitches.

void PORTD_IRQHandler(void)

{

__asm__("BKPT");

PORTD->ISFR = 0x10;

}

int main(void)

{

PCC->PCCn[PCC_PORTD_INDEX]|= PCC_PCCn_CGC_MASK; /* Enable clock for PORTD */

PORTD->PCR[4] |= PORT_PCR_MUX(1) | PORT_PCR_IRQC(9);

/* Port D4: MUX = ALT1, GPIO

* ISF flag and Interrupt when logic 1

**/

S32_NVIC->ISER[1] = (1 << (62 % 32)); // PORTD interrupt

S32_NVIC->IP[62] = 0x00; // PORTD Interrupt Priority level 0

PORTD->DFWR = 0x1F; // FILT = 31

PORTD->DFCR = 1; // CS = 1 Digital filters are clocked by the LPO clock.

PORTD->DFER = 0x00000010; // PTD4

while(1)

{

}

}Regards,

Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

I will use it, thank you very much,

Eduard.