- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

Hi,

I slightly modified the code.

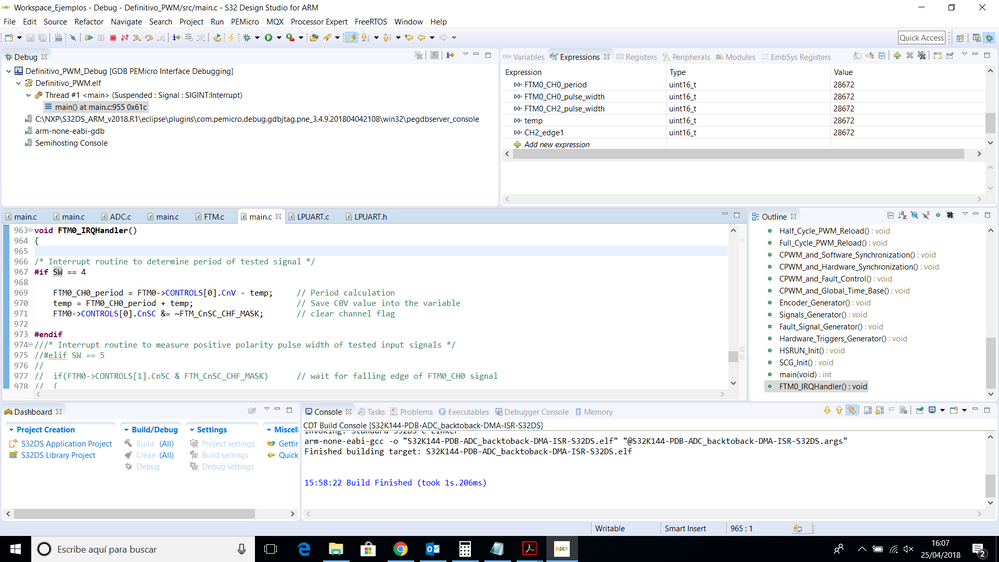

/* Interrupt routine to determine period of tested signal */

void FTM0_Ch0_Ch1_IRQHandler(void)

{

period[counter] = FTM0->CONTROLS[0].CnV - temp;

temp = FTM0->CONTROLS[0].CnV;

FTM0->CONTROLS[0].CnSC &= ~FTM_CnSC_CHF_MASK; // clear channel flag

counter++;

if((counter) == 20){

FTM1->SC = 0;

}

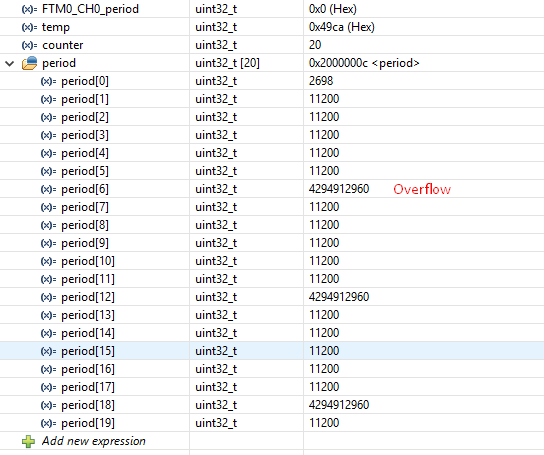

}The results:

Since

FTM1->MOD = FTM_MOD_MOD(11200 - 1); // Set Modulo (10kHz PWM frequency @112MHz system clock)the result seems to be correct.

Regards,

Daniel

I created a new project in order to allow you to compile it. I attached it below.

Yes, it is triggering and the counter is working ok, but i don't know why i can't get the results.

/*

* main implementation: use this 'C' sample to create your own application

*

*/

#include "S32K144.h" /* include peripheral declarations S32K144 */

uint32_t temp, counter, FTM0_CH0_period;

/* Transmit from RUN mode to HSRUN mode */

void HSRUN_Init()

{

SMC->PMPROT=SMC_PMPROT_AHSRUN_MASK // Allows High Speed Run

|SMC_PMPROT_AVLP_MASK; // Allows Very Low Power Modes

SMC->PMCTRL=SMC_PMCTRL_RUNM(3); // Entry to High Speed Run

/* Wait for High Speed Run mode */

while(SMC->PMSTAT != SMC_PMSTAT_PMSTAT(128))

{

}

}

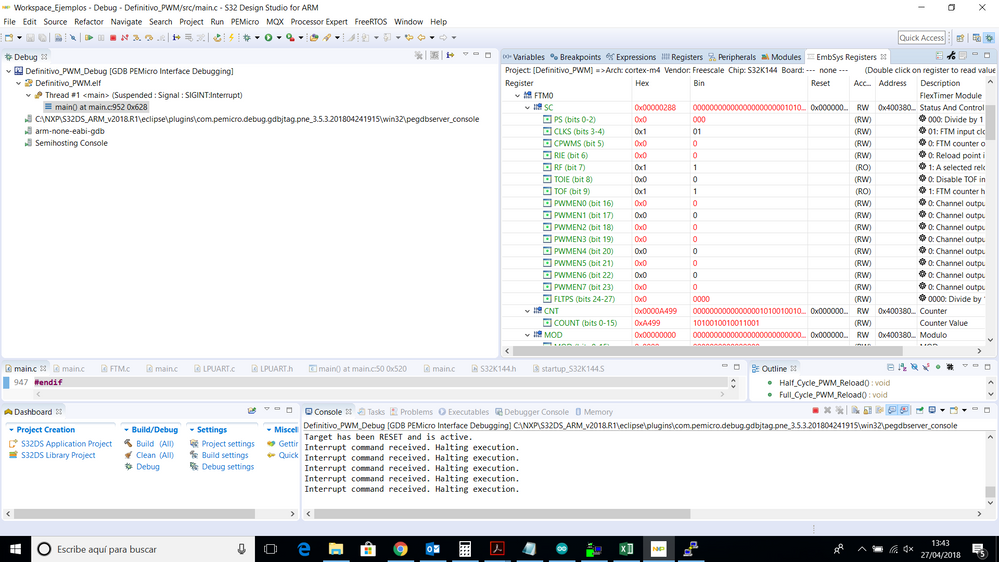

/* System oscillator and HSRUN configuration */

void SCG_Init()

{

/* SOSC Configuration

* OSC_OUT = 8MHz, 8MHz EXTAL */

SCG->SOSCDIV=SCG_SOSCDIV_SOSCDIV1(1) // System OSC DIV1=1

|SCG_SOSCDIV_SOSCDIV2(1); // System OSC DIV2=1

SCG->SOSCCFG=SCG_SOSCCFG_RANGE(2) // Medium frequency range OSC 1-8MHz

|SCG_SOSCCFG_EREFS(1); // Select internal OSC

while(SCG->SOSCCSR & SCG_SOSCCSR_LK_MASK); // Wait for SOSCCSR unlocked state

SCG->SOSCCSR=SCG_SOSCCSR_SOSCEN_MASK; // Enable OSC

// | SCG_SOSCCSR_SOSCLPEN_MASK // Enable OSC in very low power modes

while(!(SCG->SOSCCSR & SCG_SOSCCSR_SOSCVLD_MASK)); // Wait for OSC enabling and valid output

/* SPLL Configuration

* PLL_OUT = 112MHz, 8MHz EXTAL */

SCG->SPLLDIV=SCG_SPLLDIV_SPLLDIV1(1) // PLL DIV1=1

|SCG_SPLLDIV_SPLLDIV2(1); // PLL DIV2=1

SCG->SPLLCFG=SCG_SPLLCFG_PREDIV(0) // PLL PREDIV=0

|SCG_SPLLCFG_MULT(12); // PLL MULT=28

while(SCG->SPLLCSR & SCG_SPLLCSR_LK_MASK); // Wait for SPLLCSR unlocked state

SCG->SPLLCSR=SCG_SPLLCSR_SPLLEN_MASK; // Enable PLL

while(!(SCG->SPLLCSR & SCG_SPLLCSR_SPLLVLD_MASK)); // Wait for PLL enabling and valid output

/* HCCR Configuration

* PLL_OUT = 112MHz, 8MHz EXTAL */

SCG->HCCR=SCG_HCCR_SCS(6) // PLL source clock

|SCG_HCCR_DIVCORE(0) // DIVCORE=1, Core=112MHz

|SCG_HCCR_DIVBUS(1) // DIVBUS=2, BUS=56MHz

|SCG_HCCR_DIVSLOW(3); // DIVSLOW=4, Flash=28MHz

}

/* FTM1 is initialized to generate signals for Single-Edge Capture Mode of FTM0

* and Dual-Edge Capture Mode of FTM0 */

void Signals_Generator()

{

/* Enable clock for FTM1 */

PCC->PCCn[PCC_FTM1_INDEX] = PCC_PCCn_PCS(6) | PCC_PCCn_CGC_MASK;

/* Enable clock for PORTB */

PCC->PCCn[PCC_PORTB_INDEX] = PCC_PCCn_CGC_MASK;

/* Enable clock for PORTC */

PCC->PCCn[PCC_PORTD_INDEX] = PCC_PCCn_CGC_MASK;

PORTB->PCR[2] = PORT_PCR_MUX(2); // Set PTB2 for FTM1 – Channel0

PORTB->PCR[3] = PORT_PCR_MUX(2); // Set PTB3 for FTM1 – Channel1

PORTD->PCR[8] = PORT_PCR_MUX(6); // Set PTD8 for FTM1 – Channel4

PORTD->PCR[9] = PORT_PCR_MUX(6); // Set PTD9 for FTM1 – Channel5

FTM1->CONTROLS[0].CnSC=FTM_CnSC_MSB_MASK|FTM_CnSC_ELSB_MASK; // Select high-true pulses

FTM1->CONTROLS[1].CnSC=FTM_CnSC_MSB_MASK|FTM_CnSC_ELSB_MASK; // Select high-true pulses

FTM1->CONTROLS[4].CnSC=FTM_CnSC_MSB_MASK|FTM_CnSC_ELSB_MASK; // Select high-true pulses

FTM1->CONTROLS[5].CnSC=FTM_CnSC_MSB_MASK|FTM_CnSC_ELSB_MASK; // Select high-true pulses

FTM1->MOD = FTM_MOD_MOD(11200 - 1); // Set Modulo (10kHz PWM frequency @112MHz system clock)

FTM1->CONTROLS[0].CnV=FTM_CnV_VAL(2800); // Set channel Value

FTM1->CONTROLS[1].CnV=FTM_CnV_VAL(5600); // Set channel Value

FTM1->CONTROLS[4].CnV=FTM_CnV_VAL(1000); // Set channel Value

FTM1->CONTROLS[5].CnV=FTM_CnV_VAL(5600); // Set channel Value

FTM1->CNT = 0; // Counter reset

FTM1->SC|=FTM_SC_CLKS(1)|FTM_SC_PWMEN0_MASK|FTM_SC_PWMEN1_MASK|FTM_SC_PWMEN4_MASK

|FTM_SC_PWMEN5_MASK; // Select clock and enable PWM

}

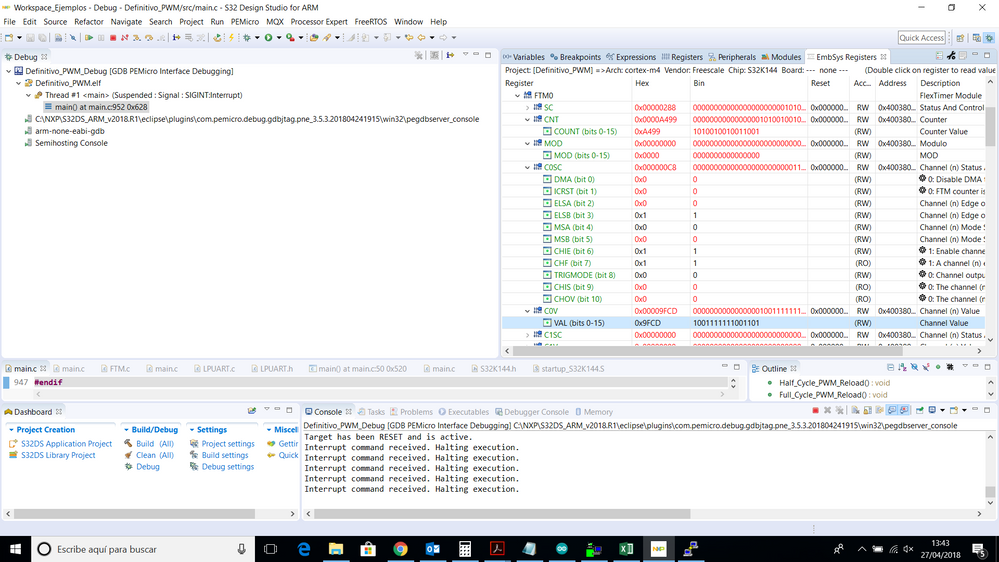

/* SW=4 - Single-Edge Capture Mode */

void FTM0_Single_Edge_Capture_Mode()

{

/* Enable clock for PORTD */

PCC->PCCn[PCC_PORTD_INDEX] = PCC_PCCn_CGC_MASK;

/* Select and enable clock for FTM0 */

PCC->PCCn[PCC_FTM0_INDEX] = PCC_PCCn_PCS(6) | PCC_PCCn_CGC_MASK;

PORTD->PCR[15] = PORT_PCR_MUX(2); // Set PTD15 for FTM0 - Channel0

S32_NVIC->ICPR[99 / 32] = 1 << (99 % 32); /* IRQ48-FTM0 ch0: clr any pending IRQ*/

S32_NVIC->ISER[99 / 32] = (1 << (99 % 32)); // Enable FTM0 interrupt

/* Input capture mode sensitive on rising edge to measure period of tested signal */

FTM0->CONTROLS[0].CnSC = 0x48u; //Falling edge 0x48u; Rising FTM_CnSC_ELSA_MASK | FTM_CnSC_CHIE_MASK (Enable Interrupt)

//Rising or Falling 0x4Cu (Enable interrupt 0x40u);

/* Reset counter */

FTM0->CNT = 0;

/* Select clock */

FTM0->SC = FTM_SC_CLKS(1);

}

void WDOG_disable (void) {

WDOG->CNT=0xD928C520; /* Unlock watchdog */

WDOG->TOVAL=0x0000FFFF; /* Maximum timeout value */

WDOG->CS = 0x00002100; /* Disable watchdog */

}

int main(void)

{

WDOG_disable();

SCG_Init();

HSRUN_Init();

/* Single-Edge Capture Mode */

Signals_Generator();

FTM0_Single_Edge_Capture_Mode();

for(;;);

}

void FTM0_IRQHandler() { /* Interrupt routine to determine period of tested signal */

counter++;

FTM0_CH0_period = FTM0->CONTROLS[0].CnV - temp; // Period calculation

temp = FTM0_CH0_period + temp; // Save C0V value into the variable

FTM0->CONTROLS[0].CnSC &= ~FTM_CnSC_CHF_MASK; // clear channel flag

}

Hi,

I slightly modified the code.

/* Interrupt routine to determine period of tested signal */

void FTM0_Ch0_Ch1_IRQHandler(void)

{

period[counter] = FTM0->CONTROLS[0].CnV - temp;

temp = FTM0->CONTROLS[0].CnV;

FTM0->CONTROLS[0].CnSC &= ~FTM_CnSC_CHF_MASK; // clear channel flag

counter++;

if((counter) == 20){

FTM1->SC = 0;

}

}The results:

Since

FTM1->MOD = FTM_MOD_MOD(11200 - 1); // Set Modulo (10kHz PWM frequency @112MHz system clock)the result seems to be correct.

Regards,

Daniel