- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am trying to get a better understanding of how the FTM syncronization works in relation to the reload points. I am using a HW trigger from SIM_FTMOPT1[FTM3SYNCBIT] to do the sync in an up-down counting mode. I currently have the CNTMIN=1 and CNTMAX=0. I also have HWRSTCNT=0.

My understanding of how this works is that when I write a 1 to the FTM3SYNCBIT, is that it would tell the FTM to load the values of MOD, CnV, OUTMASK, SWOCTRL into the registers when the FTM counter reaches CNTIN (0 in this case). However, this doesn't seem to be the case. It seems that no matter when I set the FTM3SYNCBIT to 1, the new configuration takes affect and I immediately see changes to the FTM outputs.

I am wondering if my understanding of how this works is correct?

Does my understanding of how this work apply to only certain register values that I described above, or do they all fall under the same rules in terms of how they got updated? I notice that there are different sections in the PWM synchronization chapter in the reference manual, but they are kind of confusing.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

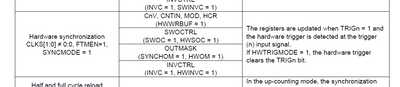

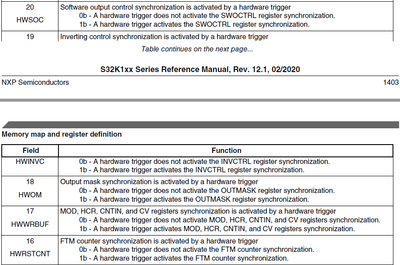

if we assume the enhanced PWM synchronization is selected then HWSOC, HWINVC, HWOM, and HWWRBUF determine if update of respective registers is activated or not. Bits do not influence when update happens. You should refer to register synchronization flowcharts in register synchronization chapters to know config bits influence. From this flowcharts can be seen that update of some registers (OUTMASK, INVCTRL, SWOCTRL) happens immediately after HW trigger, but also can happen on next loading point depending on HWRSTCNT bit, which is valid for MOD, CTIN, CnV.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I think your understanding is correct with respect of PWM synchronization, but you say that update takes effect immediately upon you write to SIM_FTMOPT1[FTM3SYNCBIT]? Not sure what is your full setting.

For more info about the update mechanism you should read chapters 47.5.12 Registers updated from write buffers and 47.5.13 PWM synchronization.

Also you can refer to below ANs where the process of updating FTM registers is explained as well

https://www.nxp.com/docs/en/application-note/AN5303.pdf

https://www.nxp.com/docs/en/application-note/AN5261.pdf

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @PetrS ,

I actually found that app note shortly after posting this question. You mentioned how my thinking of how the reload points and syncing work was correct, but after reading the app note I think what I am seeing is supposed to happen.

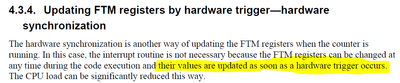

According to Table 3 in the Hardware Synchronization row in AN5303, it seems like the registers in the FTM are updated once the HW trigger is enabled and the rising edge of the trigger is received:

It also says the same thing at the beginning of section 4.3.4 of AN5303:

The configuration that I am working with has the HWSOC, HWINVC, HWOM, and HWWRBUF all set to 1 in FTMx_SYNCONF. According to the reference manual, the observed behavior that I was seeing was indeed correct.

I was confused by these bits earlier which is why I didn't mention them earlier when discussing my configuration.

Just to be clear though, these bits that are set to 1 in the FTMx_SYNCONF are what bypass the FTM loading point so that the new register values take affect immediately?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

if we assume the enhanced PWM synchronization is selected then HWSOC, HWINVC, HWOM, and HWWRBUF determine if update of respective registers is activated or not. Bits do not influence when update happens. You should refer to register synchronization flowcharts in register synchronization chapters to know config bits influence. From this flowcharts can be seen that update of some registers (OUTMASK, INVCTRL, SWOCTRL) happens immediately after HW trigger, but also can happen on next loading point depending on HWRSTCNT bit, which is valid for MOD, CTIN, CnV.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @PetrS ,

I realized my confusion had to do with OUTMASK not following the same rules as CnV when it comes to synchronization.

This question came up because I was creating this application where I had to set one signal low, and another to do an 80% duty cycle pulse. When I went to reconfigure the CnV values and OUTMASK values, the OUTMASK had every PWM channel masked. So I would update the CnV value, and then OUTMASK. However, I didn't account that if the FTM was counting up, the old CnV value would now cause this unexpected pulse that was the size of the previouse CnV value.

So it looked as if the CnV value was updating immediately, but it was just the leftover CnV value and the updated OUTMASK value causing the that channel to act on the CnV match.

This all makes sense now, and I appreciate you working through my misunderstandings.