- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

FTM - Board compatibility / working

Dear support Team,

Context:

I'm trying to use my FlexTimer module on DevBoard RevB (S32K144).

I also have the datasheet from Aug. 2015 and the new one from Aug. 2016.

I work with the IAR IDE, using the IAR library and a J-LINK Debugger.

My questions:

Is the FTM module able to work on my board (RevB)?

Or should I wait for the new board (from 2016)?

Or did I missed one or more configurations in my Code?

Note (from datasheet aug. 2015), page 801:

The Global Load mechanism of FTM module is not supported on this device.

My configurations:

It seems to approximately work when trying to Flash Code after several times and using:

• SOSC at 8MHz

• SPLL at 32MHz, that is also the System clock source (SYSclk/COREclk/BUSclk/SLOWclk set to 32MHz)

• SIRC / FIRC are disable

• FTM[0..3] clock source is SOSC_DIV1 (8MHz)

• PIN PTD15 / PTB5 set on Alteration2 to use FTM0_CH0 and FTM0_CH5 (same FTM0 Signal on this two PINs / channels)

• Need to generate a 4MHz PWM with Alpha, duty cycle = 50%

My Code (only for FTM):

Following the datasheet 2016 advice (page 1086) for my configuration. Uncalled Registers are set as Default.

int main (void)

{

Disable WatchDog

Oscillators initialization

Ports initialization

/* Needs to set MOD to get only one incrementation */

FTM0_MOD |= FTM_MOD_MOD(0x0001u);

/* Needs to set Channels MODES to edge-aligned PWM */

FTM0_C0SC |= FTM_C0SC_MSB(1u);

FTM0_C0SC |= FTM_C0SC_ELSA(1u);

FTM0_C5SC |= FTM_C5SC_MSB(1u);

FTM0_C5SC |= FTM_C5SC_ELSA(1u);

/* Needs to set CnV to get flag when Counter value is 1 */

FTM0_C0V |= FTM_C0V_VAL(0x0001u);

FTM0_C5V |= FTM_C5V_VAL(0x0001u);

/* Others configurations... */

FTM0_CNT |= FTM_CNT_COUNT(0x0000u);

FTM0_SC |= FTM_SC_CLKS(3u);

FTM0_SYNC |= FTM_SYNC_SYNCHOM(1u);

FTM0_SYNCONF |= FTM_SYNCONF_SWOM(1u);

FTM0_SYNCONF |= FTM_SYNCONF_SWRSTCNT(1u);

FTM0_SYNCONF |= FTM_SYNCONF_SYNCMODE(1u) ;

/* Enable FTM0_CH0 and FTM0_cH5 */

FTM0_OUTMASK |= FTM_OUTMASK_CH7OM(1u);

FTM0_OUTMASK |= FTM_OUTMASK_CH6OM(1u);

FTM0_OUTMASK |= FTM_OUTMASK_CH5OM(0u);

FTM0_OUTMASK |= FTM_OUTMASK_CH4OM(1u);

FTM0_OUTMASK |= FTM_OUTMASK_CH3OM(1u);

FTM0_OUTMASK |= FTM_OUTMASK_CH2OM(1u);

FTM0_OUTMASK |= FTM_OUTMASK_CH1OM(1u);

FTM0_OUTMASK |= FTM_OUTMASK_CH0OM(0u);

/* Active matching channels */

FTM0_SYNC |= FTM_SYNC_SWSYNC(1u);

FTM0_SC |= FTM_SC_PWMEN0(1u);

FTM0_SC |= FTM_SC_PWMEN5(1u);

Main Loop

Best regards,

Nadreoh

Hi,

Yes, the Global Load mechanism of FTM module is not supported on cut1 device (mask 0N77P).

The global load mechanism allows several FTM modules to have their double buffered registers synchronously reloaded after a synchronization event. In your code just FTM0 is used, so this feature is not needed.

The FTM should work. Or you do not see PWM waveform on the outputs?

BR, Petr

Thank a lot for your answer.

I have tried some others configurations to understand how to generate PWM thanks to the FlexTimers, but it's not clear to me.

What I Need

I need an 8MHz PWM Signal coming from the FlexTimer0 with a 50% duty cycle.

What I've done

- SOSC = 8MHz

- SPLL = 20 (MULT) * 8 SOSC / (2 (SPLL FACTOR) * 2 (DIV1) * (4 + 1 (PREDIV)) )

→ [16 MHz for SPLL] & [8 MHz for SPLLDIV1]

NOTE : it seems that the "+ 1" applied to the PreDivider is ignored on my board (Rev B). Is that a problem? I have to set PreDivider to 5 instead of 4 (+ 1).

- System clock is given by the SPLL clock : CORE = BUS = SLOW = SYS = 16MHz

- Using only FTM0 (same Code as above) on channel 0 (for the red LED) and channel 5 to output the signal on PIN PTB5.

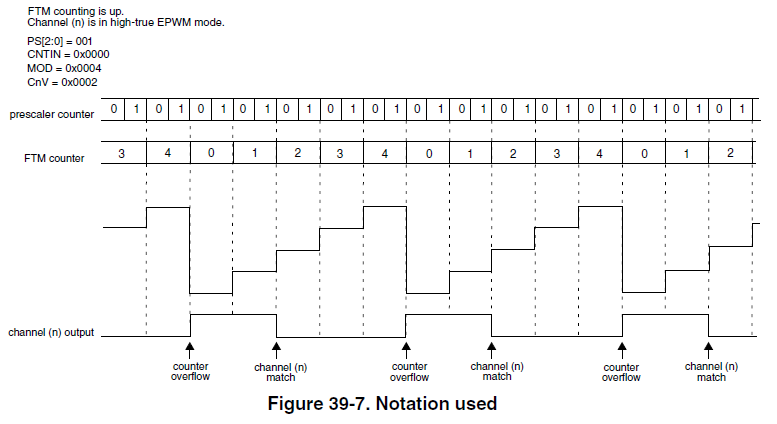

- I refered to the illustration given in the attachment to configure FTM0 as PWM with a 50% duty cycle :

FTM_MOD_MOD(0x0001u);

FTM_C5V_VAL(0x0001u);

FTM_SC_PS(0u);

FTM0_CNTIN = 0x0000ul;

What I have

With the DIV1 set to "2", I got a PWM signal of 4MHz (8MHz from SPLLDIV1 is divided by 2 because the FTM needs one clock cycle to set up and one more to set down).

I tried to set the DIV1 to "1", but this time I didn't get any signal on FTM0. Why can't I set DIV1 to "1"? Are there any limits applied on FTM, system clock, PORTB or whatever?

Best regards,

Nadreoh

Hi Nadreoh,

If external clock is selected as the FTM counter clock, then its freq must not exceed ¼ of the FTM system clock.

Try to select FTM system clock as a counter clock, using FTM0_SC |= FTM_SC_CLKS(1u), and update PWM modulo according FTM system clock.

BR, Petr

That was my missing Information :

If external clock is selected as the FTM counter clock, then its freq must not exceed ¼ of the FTM system clock.

Thank you for Reply, it works the way I want,

Nadreoh