- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

FS6503 CAN Communication

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,team

I am using FS6503, can communication can be normally used in debug mode, but can cannot communicate in operation mode. According to the operation manual, I configure CAN into operation mode, but I still can't find the problem, could you please give me some advice?

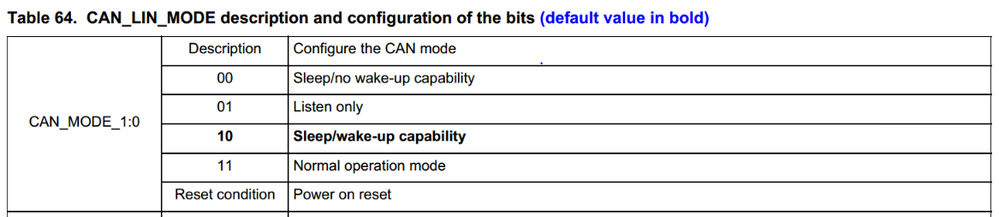

I configured CAN_LIN_MODE register, configure CAN_MODE_1:0 to "11",

the default CAN state is sleep;

fs6503 init:

fs65_status_t sbcStatus = fs65StatusOk; /* SBC return status code. */

loadUserConfig(&userConfig);

sbcStatus = FS65_Init(&userConfig);

/* Start timers for WD refresh and diagnostics */

#ifdef FS65_WD_ENABLED

WD_TIMER_START();

#endif

DIAG_TIMER_START();

// sbcStatus |= FS65_SetRegulatorState(fs65Vkam, true);

sbcStatus |= FS65_CAN_SetMode(fs65CanModeNormal, true);

return sbcStatus;

/*******************************************************************************

* FS65 configuration structures

* See description for the fs65_user_config_t structure for more information.

******************************************************************************/

static fs65_reg_config_value_t initMainRegs[] =

{

{

FS65_M_INIT_VREG_ADDR,

FS65_RW_M_VAUX_TRK_EN_NO_TRACKING | FS65_RW_M_TAUX_LIM_OFF_50_MS |

FS65_RW_M_VCAN_OV_MON_OFF | FS65_RW_M_IPFF_DIS_ENABLED | FS65_RW_M_TCCA_LIM_OFF_50_MS |

FS65_RW_M_ICCA_LIM_ICCA_LIM_OUT,

FS65_RW_M_VAUX_TRK_EN_MASK | FS65_RW_M_TAUX_LIM_OFF_MASK | FS65_RW_M_VCAN_OV_MON_MASK |

FS65_RW_M_IPFF_DIS_MASK | FS65_RW_M_TCCA_LIM_OFF_MASK | FS65_RW_M_ICCA_LIM_MASK,

false

},

{

FS65_M_INIT_WU1_ADDR,

//FS65_RW_M_WU_IO4_NO_WAKEUP | FS65_RW_M_WU_IO3_NO_WAKEUP | FS65_RW_M_WU_IO2_NO_WAKEUP |

FS65_RW_M_WU_IO4_RISING_EDGE | FS65_RW_M_WU_IO3_NO_WAKEUP | FS65_RW_M_WU_IO2_NO_WAKEUP |

FS65_RW_M_WU_IO0_RISING_EDGE,

0xFFU,

false

},

{

FS65_M_INIT_WU2_ADDR,

FS65_RW_M_LIN_SR_20KBITS | FS65_RW_M_LIN_J2602_DIS_COMPLIANT | FS65_RW_M_CAN_WU_TO_120US |

FS65_RW_M_CAN_DIS_CFG_RX_ONLY | FS65_RW_M_WU_IO5_NO_WAKEUP,

0xFFU,

false

},

{

FS65_M_INIT_INH_INT_ADDR,

FS65_RW_M_INT_INH_0_NOT_MASKED | FS65_RW_M_INT_INH_2_MASKED | FS65_RW_M_INT_INH_3_MASKED |

FS65_RW_M_INT_INH_4_NOT_MASKED | FS65_RW_M_INT_INH_5_NOT_MASKED,

FS65_RW_M_INT_INH_0_MASK | FS65_RW_M_INT_INH_2_MASK | FS65_RW_M_INT_INH_3_MASK |

FS65_RW_M_INT_INH_4_MASK | FS65_RW_M_INT_INH_5_MASK,

false

}

};

static fs65_reg_config_value_t initFailSafeRegs[] =

{

{

FS65_FS_INIT_FS1B_TIMING_ADDR,

FS65_R_FS_FS1B_TIME_106_848MS,

FS65_R_FS_FS1B_TIME_MASK,

true

},

{

FS65_FS_INIT_SUPERVISOR_ADDR,

FS65_R_FS_FS1B_TIME_RANGE_X1 | FS65_R_FS_VAUX_5D_NORMAL | FS65_R_FS_VCCA_5D_NORMAL |

FS65_R_FS_VCORE_5D_NORMAL,

0x0FU,

true

},

{

FS65_FS_INIT_FAULT_ADDR,

FS65_R_FS_FLT_ERR_IMP_RSTB | FS65_R_FS_FS1B_CAN_IMPACT_RX_ONLY | FS65_R_FS_FLT_ERR_FS_INT3_FIN6,

0x0FU,

true

},

{

FS65_FS_INIT_FSSM_ADDR,

FS65_R_FS_RSTB_DURATION_10MS | FS65_R_FS_PS_HIGH | FS65_R_FS_IO_23_FS_NOT_SAFETY |

FS65_R_FS_IO_45_FS_NOT_SAFETY,

0x0FU,

true

},

{

FS65_FS_INIT_SF_IMPACT_ADDR,

FS65_R_FS_WD_IMPACT_RSTB | FS65_R_FS_DIS_8S_ENABLED | FS65_R_FS_TDLY_TDUR_DELAY,

0x0FU,

true

},

{

FS65_FS_WD_WINDOW_ADDR,

FS65_R_FS_WD_WINDOW_512MS,

0x0FU,

true

},

{

FS65_FS_WD_LFSR_ADDR,

FS65_WD_SEED_DEFAULT,

0xFFU,

false

},

{

FS65_FS_INIT_WD_CNT_ADDR,

FS65_R_FS_WD_CNT_RFR_6 | FS65_R_FS_WD_CNT_ERR_6,

0x0FU,

true

},

{

FS65_FS_INIT_VCORE_OVUV_IMPACT_ADDR,

FS65_R_FS_VCORE_FS_UV_FS0B | FS65_R_FS_VCORE_FS_OV_RSTB_FS0B,

0x0FU,

true

},

{

FS65_FS_INIT_VCCA_OVUV_IMPACT_ADDR,

FS65_R_FS_VCCA_FS_UV_FS0B | FS65_R_FS_VCCA_FS_OV_RSTB_FS0B,

0x0FU,

true

},

{

FS65_FS_INIT_VAUX_OVUV_IMPACT_ADDR,

FS65_R_FS_VAUX_FS_UV_FS0B | FS65_R_FS_VAUX_FS_OV_RSTB_FS0B,

0x0FU,

true

}

};

static fs65_reg_config_value_t nonInitRegs[] =

{

{

FS65_M_MODE_ADDR,

FS65_RW_M_VKAM_EN_DISABLED,

FS65_RW_M_VKAM_EN_MASK,

true

},

{

FS65_M_REG_MODE_ADDR,

FS65_R_M_VCAN_EN_ENABLED | FS65_R_M_VAUX_EN_ENABLED | FS65_R_M_VCCA_EN_ENABLED |

FS65_R_M_VCORE_EN_ENABLED,

FS65_R_M_VCAN_EN_MASK | FS65_R_M_VAUX_EN_MASK | FS65_R_M_VCCA_EN_MASK |

FS65_R_M_VCORE_EN_MASK,

true

},

{

FS65_M_IO_OUT_AMUX_ADDR,

FS65_RW_M_AMUX_VREF | FS65_RW_M_IO_OUT_4_LOW | FS65_RW_M_IO_OUT_4_EN_Z,

FS65_RW_M_AMUX_MASK | FS65_RW_M_IO_OUT_4_MASK | FS65_RW_M_IO_OUT_4_EN_MASK,

false

},

{

FS65_M_CAN_LIN_MODE_ADDR,

FS65_RW_M_LIN_AUTO_DIS_RESET | FS65_RW_M_LIN_MODE_NORMAL | FS65_RW_M_CAN_AUTO_DIS_RESET |

FS65_RW_M_CAN_MODE_NORMAL,

FS65_RW_M_LIN_AUTO_DIS_MASK | FS65_RW_M_LIN_MODE_MASK | FS65_RW_M_CAN_AUTO_DIS_MASK |

FS65_RW_M_CAN_MODE_MASK,

false

}

};

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Please take a closer look at our AN5238 where you can find the recommended start-up SPI sequence (Chapter 14.2). As you can notice, we use the 0xB0C0 command (CAN_MODE_1:0 = 0b11) to enable normal CAN operation mode after 7x good WD refresh (the 1st good WD refresh closes INIT_FS & the 7th good WD refresh clears the FLT_ERR_CNT)).

Keep in mind that the first watchdog refresh (0x4D when using a default LFSR value of 0xB2) must happen before INIT_FS timeout (256ms). Then you need to periodically refresh the watchdog during every open window of the window period (set using WD_WINDOW_3:0 bits). If you would not like to use watchdog, use WD disable (WD_WINDOW_3:0 = 0b0000) in INIT_FS phase (256 ms open window after releasing RSTB) and then close INIT_FS phase by 1 good WD refresh (0x4D when using a default LFSR value of 0xB2). Then no further watchdog refresh is necessary.

You might also find useful an example project available at Embedded SW: FS65/FS45 SW Driver | NXP

I hope it helps.

Best regards,

Tomas