- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Could you explain how it's work EIM Module?

Could you explain how it's work EIM Module?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Could you explain how it's work EIM Module?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

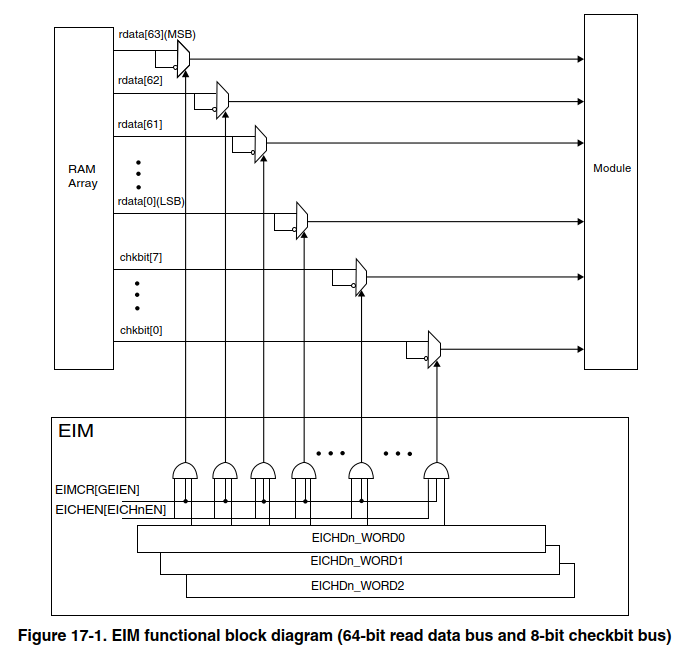

It's necessary to implement memory protection in our project and I started from example ( eim_injection_s32k116 ). Honestly, I'm a little bite confuse. I didn't understand how it's work EIM Module and what represent this structure:

typedef struct

{

uint8_t channel; /*!< EIM channel number */

uint8_t checkBitMask; /*!< Specifies whether the corresponding bit of the check-bit bus

from the target RAM should be inverted or remain unmodified */

uint32_t dataMask; /*!< Specifies whether the corresponding bit of the read data bus

from the target RAM should be inverted or remain unmodified */

bool enable; /*!< true : EIM channel operation is enabled

false : EIM channel operation is disabled */

} eim_user_channel_config_t;

In project is used one address ( /* Initialize address used to test */ ). How impact this address EIM and ERM module? I know that ERM_DRV_GetErrorDetail() return this address like error but how and why?

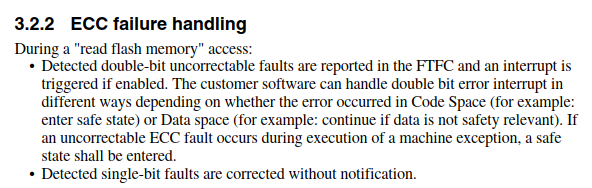

Also, ERM Module on S32K116 is just for SRAM_U Memory. How I can detect error on ROM and NVM ?

Thank you in advance,

Catalin Stiuca

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

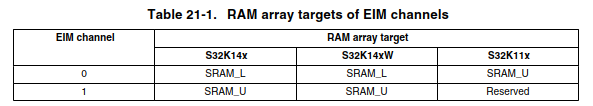

Hi, ERM modules invert certain line on the data bus, causing erratic read of certain address. It is needed to choose the channel fitting to address range of target memory where an ECC error is injected. EIM only use RAM arrays (on some other devices it can be local RAM arrays as FEC or DMA).

According S32K safety manual, flash ECC error are detected by flash controller:

Hope it helps a bit