- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Cortex M0+ delay routine without timers

Cortex M0+ delay routine without timers

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Cortex M0+ delay routine without timers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

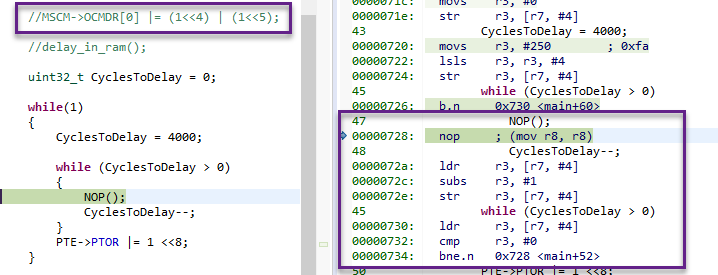

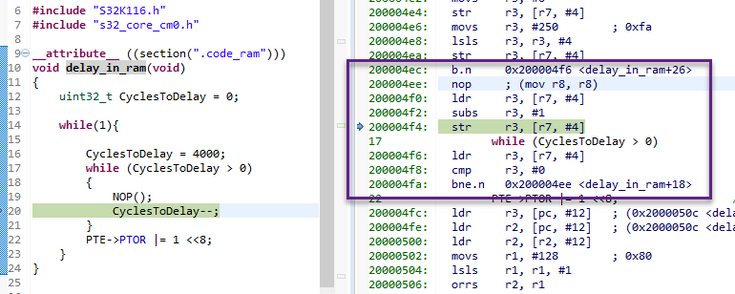

Hello, I´m trying to implement a small assembly routine in a cortex M0+ in order to introduce a software controlled delay in microseconds. For performing this, i wrote this small while() routine:

So, knowing exactly what assembly instructions are executing, the clk clock frequency, and the number of clk cycles per instruction, I can calculate the CyclesToDelay value for a desired delay to introduce.

Assembly:

__no_operation();

0002 73F8 NOP

CyclesToDelay--;

0002 73FA LDR R1, [R0]

0002 73FC SUBS R1, R1, #1

0002 73FE STR R1, [R0]

while (CyclesToDelay > 0)

0002 7400 LDR R1, [R0]

0002 7402 CMP R1, #0

0002 7404 BNE 0x000273F8

Instruction clk cycles according https://developer.arm.com/documentation/ddi0432/c/programmers-model/instruction-set-summary are:

NOP 1 clk cycles

LDR 2 clk cycles

SUBS 1 clk cycles

STR 2 clk cycles

LDR 2 clk cycles

CMP 1 clk cycles

BNE 3 clk cycles

Total clk cycles in this routine = 12 clk cycles,

CORE_CLK = 48mhz

Then,

1) 1 CORE_CLK cycle = 1 / 48 us

2) 12 CORE_CLK cycles = 12/48 us ( The number of microseconds one loop of this routine should delay)

Finally:

3) CyclesToDelay * (12/48) = delay_we_want_to_introduce(us)

or

CyclesToDelay = delay_we_want_to_inject(us) * 48 / 12

However, measuring the delays obtained with this method does not seem to be very accurate. I dont know if this is going to be deterministic or if this is totally possible in this Cortex M0+. Feedback would be appreciated. Many thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @riglesias2021,

It does not depend just on the core.

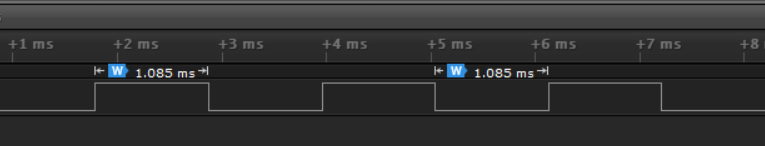

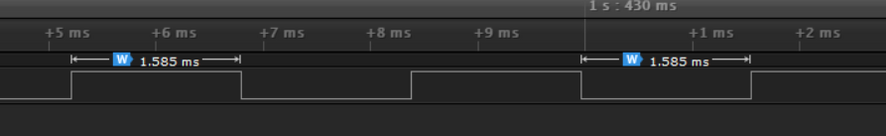

Although the S32K11x series is not that complicated, we can get different results when

- the delay code is placed in SRAM:

PTE8 Toggles every 0.9177ms instead of 1ms

- In Flash with Prefetch buffer enabled: 1.085ms

- In Flash with Prefetch buffer disabled: 1.585ms

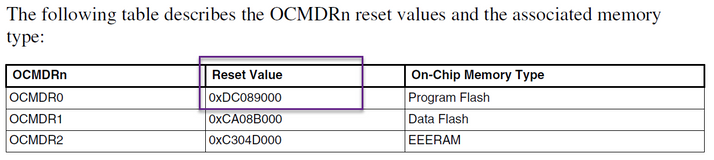

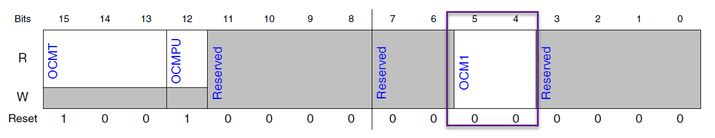

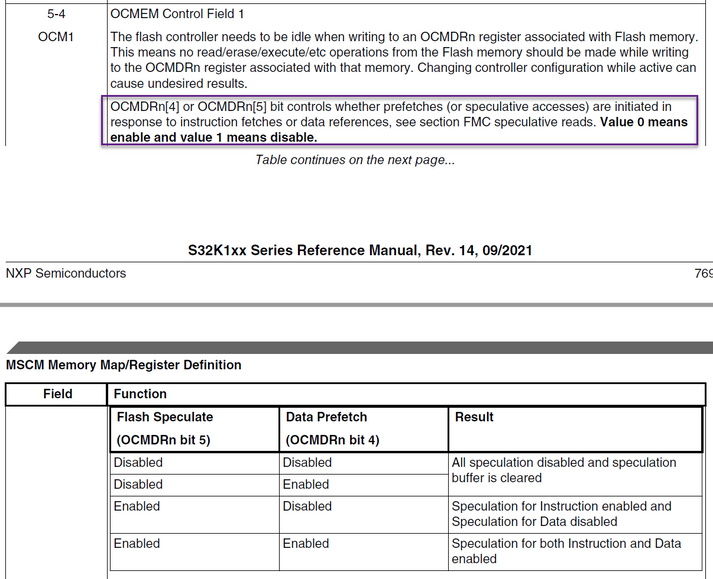

MSCM->OCMDR[0] |= (1<<4) | (1<<5);

Please refer to the RM, Section 35.5.2 Speculative reads for more information about the buffer.

Regadrs,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@danielmartynek Thanks for the reply, It seems that i dont have the Prefetch buffer enabled, Its is possible to determine with exactitude the delay of this routine with a specific MSCM config?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @riglesias2021,

The prefetch buffer is enabled by default.

But anyway, I don't think we can determine the accuracy of the timing.

Even with the prefetch buffer disabled, it depends on the location of the code in the flash.

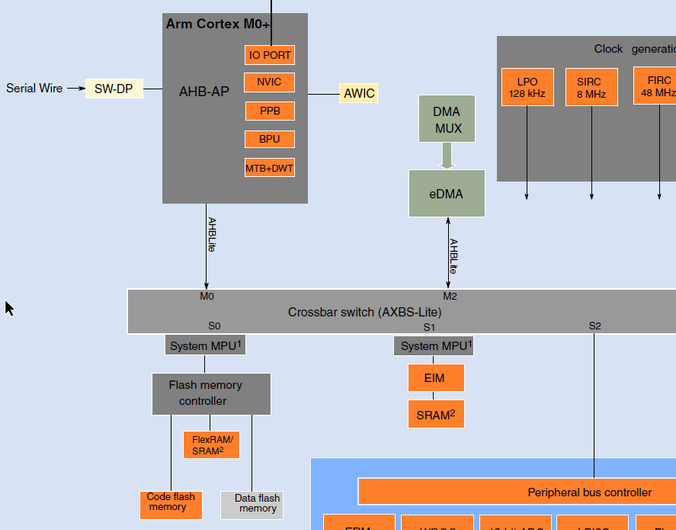

Also, the core accesses the Flash via the Crossbar switch.

The eDMA could add other wait states because of the arbitration on the switch,

I would recommend using HW timers.

Regards,

Daniel