- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

There is difficulty entering VLPS mode in SPLL mode.

Our project is using the SPLL -> FIRC -> VLPS mode entry procedure.

The SCG status is attached below.

<SPLL>

<SPLL -> FIRC>

After adding OSIF_TimeDelay in this modification, it is impossible to enter VLPS mode. (Trace32 debugger attached)

However, it was confirmed that VLPS mode was entered normally when the debugger was disabled.

For some reason, I cannot enter VLPS mode with the debugger connected?

I am inquiring because I cannot find information in the reference manual.

thank you

已解决! 转到解答。

Hi

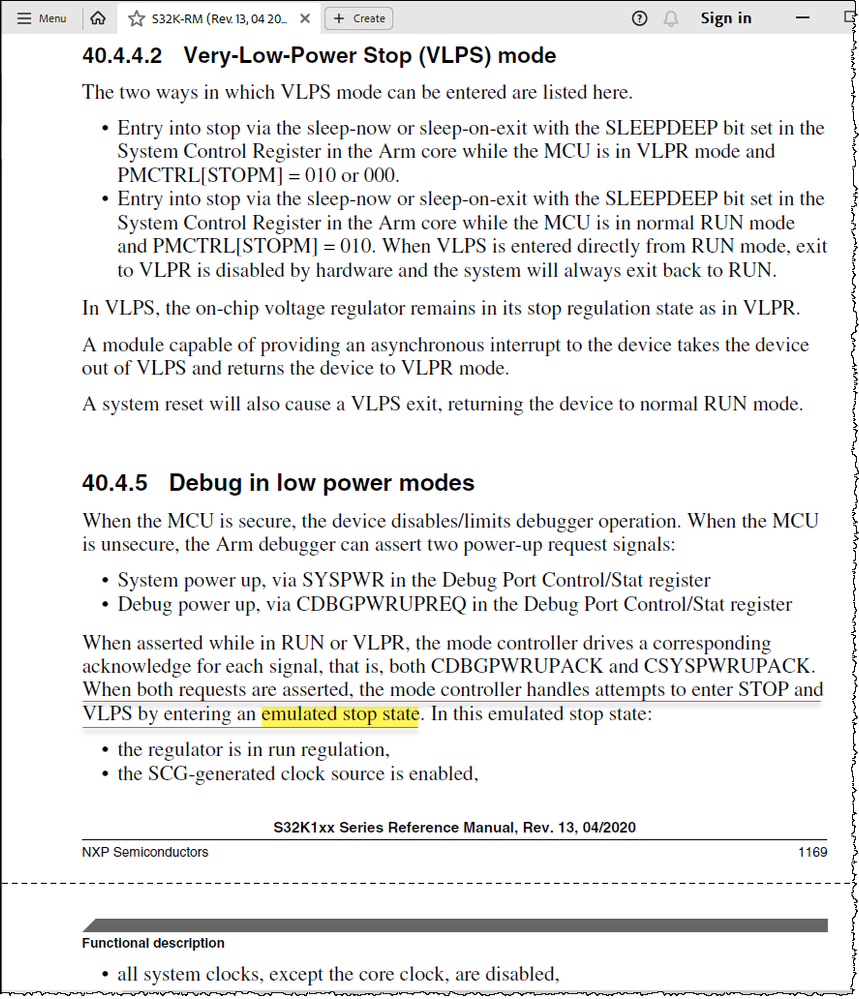

Please read the 40.4.5 Debug in low power modes of S32K1xx MCU Family - Reference Manual.

When both requests are asserted, the mode controller handles attempts to enter STOP and VLPS by entering an emulated stop state.

7.3. Tips for making low-power measurements on the bench of AN5425 Power Management for S32K1xx also suggest that you should: Disconnect the debugger and power cycle the MCU

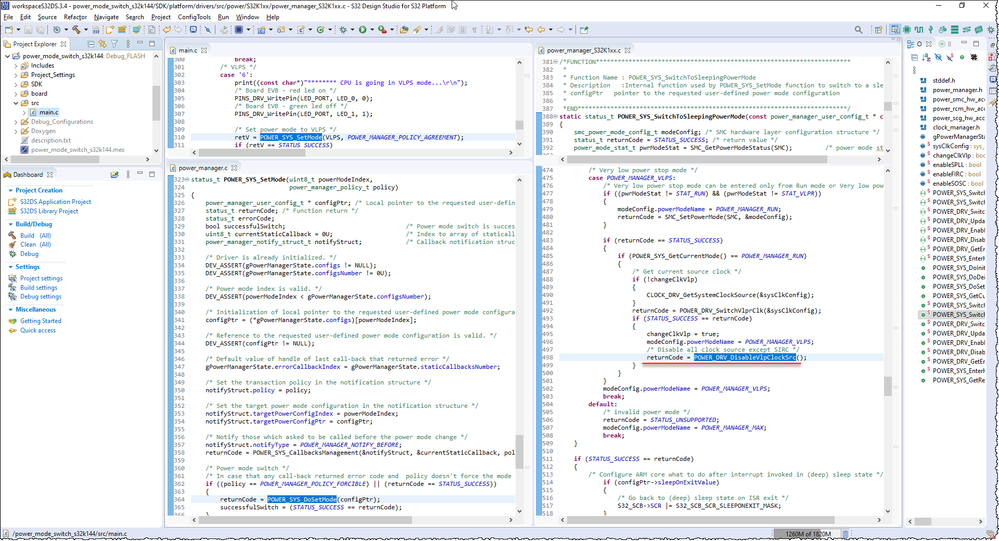

Please refer to the power_mode_switch_s32k144 example in S32K1 SDK.(for example: S32K1 SDK RTM4.0.3 in S32DS v3.4)

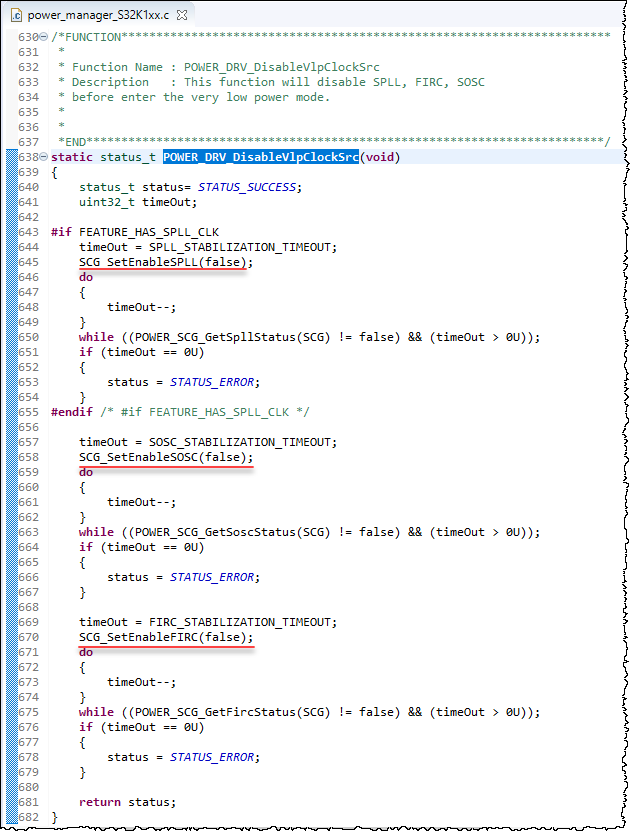

As you can see, it will disable SPLL\FIRC\SOSC at line 498 returnCode = POWER_DRV_DisableVlpClockSrc(); by SCG_SetEnableSPLL(false); and SCG_SetEnableFIRC(false);

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi

Please read the 40.4.5 Debug in low power modes of S32K1xx MCU Family - Reference Manual.

When both requests are asserted, the mode controller handles attempts to enter STOP and VLPS by entering an emulated stop state.

7.3. Tips for making low-power measurements on the bench of AN5425 Power Management for S32K1xx also suggest that you should: Disconnect the debugger and power cycle the MCU

Please refer to the power_mode_switch_s32k144 example in S32K1 SDK.(for example: S32K1 SDK RTM4.0.3 in S32DS v3.4)

As you can see, it will disable SPLL\FIRC\SOSC at line 498 returnCode = POWER_DRV_DisableVlpClockSrc(); by SCG_SetEnableSPLL(false); and SCG_SetEnableFIRC(false);

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------