- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I develop ECU related CAN FD by using S32K144.

My product CAN FD baud rate requirement is 2Mbps.

CAN FD is not working in only 2Mbps.

I changed baud rate variously as 500kbps, 1Mbps, 1454kbps, 1777kbps.

But CAN FD is working well in all condition except for 2Mbps.

Below is setting of CAN FD for 2Mbps

<Processor expert of S32 Design studio>

1) PE clock source : Sys clock (40 MHz)

2) Arbitration Phase

- Propagation segment : 7

- Phase segment 1 : 6

- Phase segment 2 : 3

- Prescaler Division Factor : 3

- Resync jump width : 1

- Bitrate : 500kbps

- Sampling point : 80%

3) Data Phase

- Propagation segment : 11

- Phase segment 1 : 3

- Phase segment 2 : 3

- Prescaler Division Factor : 0

- Resync jump width : 1

- Bitrate : 2000kbps

- Sampling point : 80%

<Network Hardware Configuration of CANoe>

1) Mode : CAN FD

2) Arbitration phase

- Baud rate : 500kbps

- Sampling point : 80%

3) Data phase

- Baud rate : 2000kbps

- Sampling point : 80%

Thank you.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaewoo,

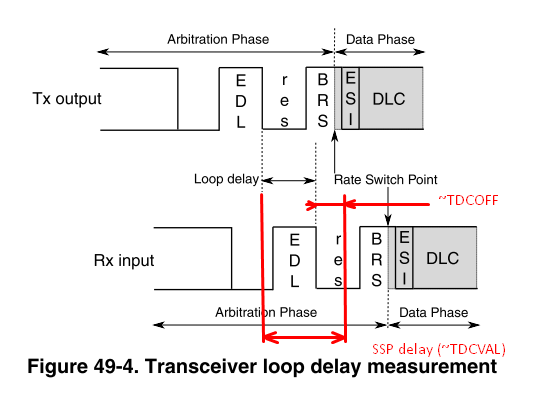

do you have Transceiver Delay Compensation enabled (FDCTRL[TCDEN]=1)?

If yes, what is FDCTRL setting in fact. What is read from FDCTRL[TDCVAL]?

If not (FDCTRL[TCDEN]=0) then the bit time setting should work, I think.

What is the transceiver used on your application?

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaewoo,

do you have Transceiver Delay Compensation enabled (FDCTRL[TCDEN]=1)?

If yes, what is FDCTRL setting in fact. What is read from FDCTRL[TDCVAL]?

If not (FDCTRL[TCDEN]=0) then the bit time setting should work, I think.

What is the transceiver used on your application?

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr

Thank you for your response.

I did not use TDC function. So I enable TDCEN. And set the TDCOFF.

And then CAN FD is working well for 2Mbps. But I wonder one point.

I change the TDCOFF value variously. Error frame occurs depending on the TDC value.

Now I set the TDCOFF(5), do not occur Error frame. How do I set the proper TDCOFF value ?

void FLEXCAN_HAL_SetTDCEN(CAN_Type * base)

{

/* Debug mode, Halt and Freeze*/

FLEXCAN_HAL_EnterFreezeMode(base);

/* FDRATE=1: enable Bit Rate Switch */

/* TDCEN=1 : enable Transceiver Delay Compensation */

/* TDCOFF=5: 5 CAN clocks offset used */

base->FDCTRL = CAN_FDCTRL_FDRATE(1) | CAN_FDCTRL_TDCEN(1) |

CAN_FDCTRL_TDCOFF(5) | CAN_FDCTRL_MBDSR0(1);

/* De-assert Freeze Mode */

FLEXCAN_HAL_ExitFreezeMode(base);

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaewoo,

Theoretically the offset should be set to the middle of the data bit time, so

TDCOFF = bit_time/2 * PEclock = 225ns * 40MHz = 9.

The best approach is using a "trial and error" method to realistically find the delay value, sure it is suitable for development phase only. Set TDCOFF from 0 to max value and find the range when message is sent without error, then set TDCOFF to median of the range.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr

I have additional question for secondary sample point.

I understood that your calculation -> (TDCOFF = bit_time/2 * PEclock = 225ns * 40MHz = 9.)

And secondary sample point is defined that measured loop delay time added to TDCOFF value

in S32K reference manual.

Finally first sample point is 80%. And what is value of secondary sample point ?

How do I calculate the secondary sample point in [%] ?

Thank you.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaewoo,

The FDCTRL[TDCVAL] specifies secondary sample point position. The value is an integer multiple of the PE clock.

Thus

SSPdelay = TDCVAL / PEclock [s]

If you want to have result in % use

SSP = SSPdelay * bitrate * 100 [%]

However you can easily get the value above 100% depending on actually measured transceiver loop delay.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Petr

Thank you for response.

For example, CAN setting as below.

1) Clock : 40Mhz

2) TQ : 20 TQ

3) Sample point : 80%

4) TDCVAL : 10

5) bitrate : 2Mbps (period : 500ns)

SSPdelay = TDCVAL / PEclock [s]

= 10 x 25ns(40Mhz)

= 250ns

SSP = SSPdelay * bitrate * 100 [%]

= 250ns / 500ns(2Mbps) * 100 [%]

= 50%

Actually First smaple point is 80% (500ns x 80 / 100). So bit sample timing is 400ns.

And Secondary sample point is that First sample point + SSPdelay (650ns = 80%(400ns) + 50%(250 ns) )

Above calculation is right ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jaewoo,

Your calculation is correct except of the last one.

There is no combination of both sample points. Either regular sample point is used, if TDC is disabled, or secondary sample point is used instead, if the TDC is enabled.

The SSP must be used if the transceiver loop delay is greater than a bit time, so the MCU cannot sample the same bit that is transmitted.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for response.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your response.