- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: Basics of Bus Fault in S32DS Program

Basics of Bus Fault in S32DS Program

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi team,

I was trying to run a simple complementary program on a S32K358 microcontroller using the S32DS IDE. But i'm facing an error called as bus fault in the program. I have attached the highlighted screenshot of the error message below.

I ran the same program in an S32K344 evaluation board and there I didn't face such an error. Please explain me this fault and also the solution to this as I'm new to this IDE's programming. It would be really helpful.

S32DS-S32PLATFORM #S32K358 #BusFault

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

You were right about the failure in the Clock_Ip_init() function. The problem was not with the hardware. The problem was in specifying the right clock frequency in the FXOSC section in the clock configuration tool (which makes the Clock_Ip_init() function). My custom hardware was using 40 MHz oscillator and I was running the code in 16 MHz FXOSC in the clock configuration tool of my program. Once I changed that to 40 MHz and uploaded the code again, the busfault error was gone and the code was running.

Thanks for all the help you have given me sir. I deeply appreciate it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

In a new custom project file, I'm now experiencing this type of bus and hard fault with the message highlighted as shown,

I haven't connected any peripherals or devices to the custom microcontroller. Do you think that the fault is due to the SPI data not being transmitted/received to the controller? Or is it something else?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you share a picture of the Debug tab displayed on the left side of the S32DS during debugging? This tab shows where the code failed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @VaneB,

Here is the screenshot of the right side of debug window you requested.

What could be the problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

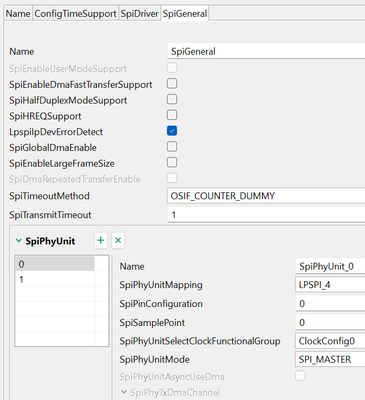

It seems that your code fails in the Lpspi_Ip_UpdateTransferMode() function. How do you call this function? Also, could you share the SPI configurations?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

This is the Lpspi_Ip_UpdateTransferMode() function in my code

Lpspi_Ip_StatusType Lpspi_Ip_UpdateTransferMode(uint8 Instance, Lpspi_Ip_ModeType Mode)

{

Lpspi_Ip_StateStructureType* State;

Lpspi_Ip_StatusType Status = LPSPI_IP_STATUS_SUCCESS;

#if (LPSPI_IP_DMA_USED == STD_ON)

Dma_Ip_LogicChannelTransferListType DmaTcdList[1u];

#endif

#if (LPSPI_IP_DEV_ERROR_DETECT == STD_ON)

DevAssert(Instance < LPSPI_INSTANCE_COUNT);

#endif

State = Lpspi_Ip_apxStateStructureArray[Instance];

#if (LPSPI_IP_DEV_ERROR_DETECT == STD_ON)

DevAssert(NULL_PTR != State);

#endif

/* Transfer mode can be changed when no transfers are in progress. */

if (State->Status != LPSPI_IP_BUSY)

{

State->TransferMode = Mode;

#if (LPSPI_IP_DMA_USED == STD_ON)

if (TRUE == State->PhyUnitConfig->DmaUsed)

{

/* Activate TX DMA and RX DMA interrupt in interrupt mode or disable then in polling mode. */

DmaTcdList[0u].Param = DMA_IP_CH_SET_CONTROL_EN_MAJOR_INTERRUPT;

switch (State->TransferMode)

{

case LPSPI_IP_POLLING:

/* Disable DMA major interrupt. */

DmaTcdList[0u].Value = 0u;

break;

case LPSPI_IP_INTERRUPT:

/* Enable DMA major interrupt. */

DmaTcdList[0u].Value = 1u;

break;

default:

/* Nothing to do */

break;

}

(void)Dma_Ip_SetLogicChannelTransferList(State->PhyUnitConfig->TxDmaChannel, DmaTcdList, 1u);

(void)Dma_Ip_SetLogicChannelTransferList(State->PhyUnitConfig->RxDmaChannel, DmaTcdList, 1u);

}

#endif

}

else

{

Status = LPSPI_IP_STATUS_FAIL;

}

return Status;

}

The below mentioned are the SPI configurations,

SpiDriver

SpiGeneral

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I sent you a private message

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

I ran the Emios_PWM_Ip example code, that comes with the SDK, on my custom board with the S32K358 controller. I'm still getting the same HardFault error mentioned before. What could be the problem then?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

BusFault: detects memory access errors on instruction fetch, data read/write, interrupt vector fetch, and register stacking (save/restore) on interrupt (entry/exit).

HardFault: is the default exception and can be triggered because of an error during exception

processing, or because an exception cannot be managed by any other exception mechanism.

If there is no handler for a specific fault, it is escalated to HardFault.

As the code works with a S32K344, there could be a configuration problem. If it is possible could you share your project or configurations? Also, which RTD version are you using?

BR, VaneB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

I have attached the .zip file of the project that the code is in. I'm using version 4.0.0 of PlatformSDK kit from NXP.

P.S.: Is it necessary to use both Cortex-M7_0_0 (Boot) and Cortex-M7_0_2 files for programming S32K358? Why does the design studio make two files for this processor and only one file for S32K344??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have flashed your code on my S32K3X8EVB-Q289 and I did not get a bus Fault. Are you using a custom board?

Is it necessary to use both Cortex-M7_0_0 (Boot) and Cortex-M7_0_2 files for programming S32K358? No, depends if you want to work with multicore.

Why does the design studio create two files for this processor and only one file for S32K344? Because S32K358 devices have 1 LS core and 1 single core and S32K344 devices have only 1 LS core. So one project is created for each device core.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

Yes, you are right. I'm using a custom made board which uses the S32K358. What may the problem then?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems to be a hardware problem. Since the Hard fault occurs during clock initialization, a possible root cause could be the connections of the EXTAL and XTAL pins, for this you can use as a reference the Hardware Design Guidelines for S32K3xx Microcontrollers.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

As per the Hardware Design Guidelines for S32K3xx Microcontrollers the crystal oscillator design of our hardware seems to be correct. What could be other possible hardware/software reason(s) for the BusFault and HardFault errors?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the shared images I deduce that it is a clock problem because the failure occurs in the Clock_Ip_init() function. To verify if this is the case, test the Clock_Ip_Example_S32K358 making the necessary changes to match your HW.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @VaneB

You were right about the failure in the Clock_Ip_init() function. The problem was not with the hardware. The problem was in specifying the right clock frequency in the FXOSC section in the clock configuration tool (which makes the Clock_Ip_init() function). My custom hardware was using 40 MHz oscillator and I was running the code in 16 MHz FXOSC in the clock configuration tool of my program. Once I changed that to 40 MHz and uploaded the code again, the busfault error was gone and the code was running.

Thanks for all the help you have given me sir. I deeply appreciate it.