- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

BIST Query of S32K312

Hello,

Currently, I am working on BIST module of S32K312. I am using S32k312EVB-Q172 Board, PE Micro Debugger and S32DS. Using RTD S32K3_RTD_3_0_0_P07_D2306_ASR_REL_4_7_REV_0000_20230629.

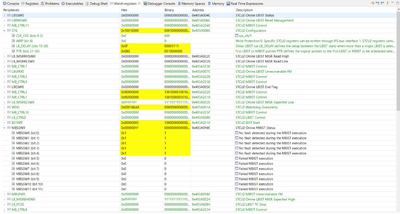

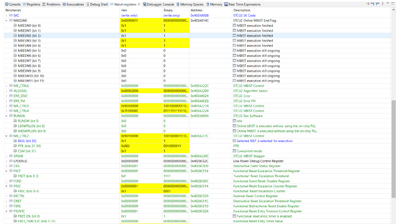

After calling of Bist_Run(BIST_DIAGNOSTIC_CFG), Online BIST test is running. and generating functional reset, I am also attaching screenshot of register status of STCU2 module please see.

Query on below Points.

1. After functional reset how to come in normal program execution.

2. After injecting the fault through EIM single bit ERM ISR called and not doing functional reset it is generating exceptions. then how can i get the fault status through BIST module.

3. First need to inject the error or first we should need to call bist_run function for self-test module test.

4. According to S32K3XXRM ST_DONE bit of FES register should be set. but my case it is not setting. ST_DONE bit is indicating self-test done successfully.

Please give me support on above points.

Please find the attached file for more clarification.

Thanks,

@BIST, @S32K312, @functional reset, @EIM, @FCCU, @ERM,

Hello,

1. After functional reset how to come in normal program execution.

Not sure what you define as normal. But after functional reset the device will boot from reset phase, so all configurations, memory inits, etc.. need to be done as after any other functional reset.

2. After injecting the fault through EIM single bit ERM ISR called and not doing functional reset it is generating exceptions. then how can i get the fault status through BIST module.

BIST module and ERM module are 2 different modules, which are not related. BIST has its own result registers.

3. First need to inject the error or first we should need to call bist_run function for self-test module test.

Are you referring to injecting BIST error into selftest? This is not possible from SW.

4. According to S32K3XXRM ST_DONE bit of FES register should be set. but my case it is not setting. ST_DONE bit is indicating self-test done successfully.

Does your online BIST finish successfully? Do you see any failed execution or errors in ERR_STAT?

Best regards,

Peter

Hello @petervlna

Thanks for your quick response.

Yes, online BIST finish successfully, after completion doing functional reset but same time my expectation is ST_DONE bit in FES register should be high. please see the attachment register details.

I am trying to perform above s32k312 BIST test case which is provided in S32K3XX_SAF_BIST.pdf

My Query on above test case.

1. After call of step1 function reset is generated. then how we can perform setp2.

2. If I am injecting error through EIM or FCCU on step3, ERM or FCCU Alarm interrupt will generate, this step needs to perform after successfully perform of setp1.

After doing of step1, I am getting below attached BIST register details and FES register details.

Could you please provide me example code and application notes for BIST module.

I am looking forward for your response.

Thanks

Hello,

Yes, online BIST finish successfully, after completion doing functional reset but same time my expectation is ST_DONE bit in FES register should be high. please see the attachment register details.

In past such flag was set on offline BIST. I am not sure how it is implemented here, but since we have only one STCU2 module across micro families, I expect it will be the same.

I am trying to perform above s32k312 BIST test case which is provided in S32K3XX_SAF_BIST.pdf

I am not familiar with SAF_BIST.pdf. I was looking for in it in SAF package with no luck.

1. After call of step1 function reset is generated. then how we can perform setp2.

Yes this is correct, as after BIST memories and peripherial registers are full of test patterns, So reset is needed to restore the default register values and initialize memories.

I am afraid you missunderstood the point of the tests. It is not runtime BIST fault injection. It will test reporting paths from STCU to FCCU.

You will only injects error into error status register of STCU and not physically into tests.

I can answer you the HW mechanisms itself, but for the SAF software implementation of the routines, etc... which control the HW logic, please rise a ticket on NXP web page, so the author of the SW routines can give you the most accurate answer.

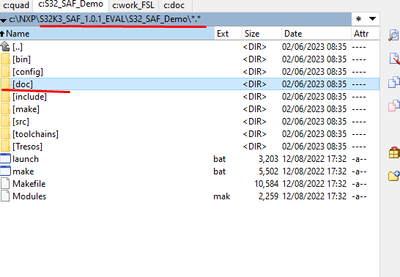

Could you please provide me example code and application notes for BIST module.

Demo is part of the SAF module along with documentation:

Best regards,

Peter

Hello,@petervlna

I am afraid you missunderstood the point of the tests. It is not runtime BIST fault injection. It will test reporting paths from STCU to FCCU.

If we are unable to artificially create a BIST error before running the BIST,

1. how should I verify the functionality of the BIST ?

2. and the handling mechanism between STCU2 and FCCU during BIST execution?

I am looking forward for your response.

Thank you very much!

Hello,

1. how should I verify the functionality of the BIST ?

I expect that this is covered by testing process in the factory as part of ISO.

As all the ASIL-D ECUs out there, are not doing any additional tests.

But if you want exact answer you will need to submit a ticket and NXP.com so the question will reach the HW team.

2. and the handling mechanism between STCU2 and FCCU during BIST execution?

FCCU is also tested during BIST. So no reporting is done. FCCU status will be loaded from STCU ERR after reset.

Best regards,

Peter