- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- ADC slef Test

ADC slef Test

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC slef Test

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Project Overview

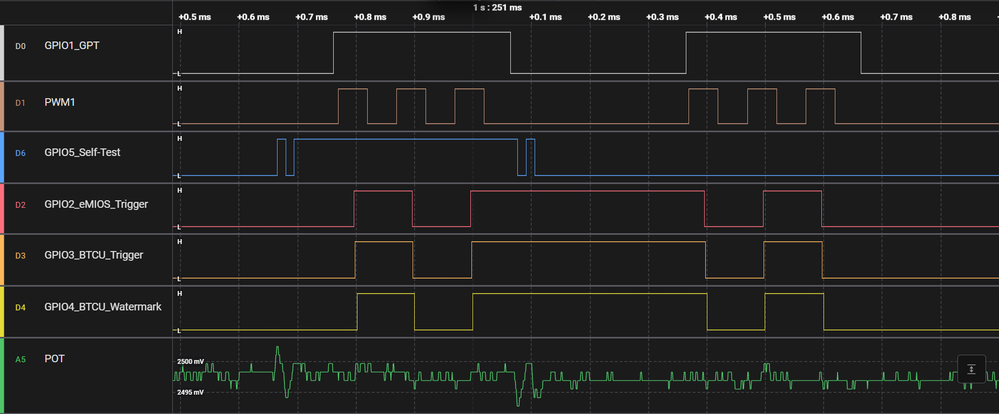

I’m working on a design where ADC sampling is triggered through an eMIOS → BCTU → ADC chain. The BCTU receives triggers from eMIOS PWM channels configured in OPWMT mode to create precise timing offsets between trigger events.

Current Setup

- ADC0 processes two groups of signals:

- Group 1 (two ADC channels) triggered by eMIOS_0_CH1

- Group 2 (two ADC channels) triggered by eMIOS_0_CH2

- Each signal sample takes about 1.3 µs, so each group requires approximately 2.6 µs.

- The second group (triggered by CH2) is offset by 3.6 µs (+1 µs margin) to avoid overlap with the first group.

Timing sequence:

Time (µs): 0 1.3 2.6 3.6 4.9 6.2 7.2

|----------|----------|----------|----------|----------|----------|----------|

eMIOS_0_CH1 ---> adc_ch1 (start at 0 µs)

---> adc_ch2 (after 1.3 µs)

eMIOS_0_CH2 (offset by 3.6 µs)

---> adc_ch1 (start at 3.6 µs)

---> adc_ch2 (after 1.3 µs → ~4.9 µs)

eMIOS_0_CH4 (offset by 7.2 µs)

---> software trigger for ADC0 self-test- After both groups complete, I added eMIOS_0_CH4 as a software trigger (via callback) to start an ADC self-test on ADC0.using the Adc_Sar_Ip_SelfTest API

- CH4 is offset by 7.2 µs to ensure all sampling is complete before the self-test begins.

Observation

When I toggle a GPIO in the CH4 callback, it fires as expected. However, running the ADC self-test for a single ADC instance takes about 13 µs (measured in software).

Question

- Is this self-test duration (~13 µs) expected for S32K3xx ADC (Algorithm S + C)?

- My calculations:

- Sampling Phase Time (ST) = 23

- Evaluation Time per bit = 4

- Data Processing Time (DP) = 2

- What is the best way to schedule the self-test without impacting the 25 µs acquisition cycle? Are there alternative or more efficient methods to trigger self-tests for ADCs, considering that each instance may contain multiple ADC channel groups? I'm currently using the Adc_Sar_Ip_SelfTest API from the RTD, and I would like to know whether it's more appropriate to perform the self-test during initialization, at runtime, or both. What are the best practices for handling ADC self-tests in terms of timing, reliability, and overall system performance?

- Would masking only ADC0 triggers (instead of freezing all BCTU triggers) be the right approach to keep ADC1 and ADC2 running during the self-test?

Goal: Ensure periodic self-test on ADC0 without disturbing the real-time sampling of other ADCs.

I have attached my project so you can have a look.

s32k344

RTD_6.0.0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your interest in our products and for contributing to our community.

According with 60.3.17.2 Self-test section: Individual steps can take up to 1 µs at 80 MHz ADC clock frequency.

Please find attached example. In practice, I cannot get less than 14us per instance.

For safety applications, it is important to verify correct operation at regular intervals. But also consider that the ADC Self-Test function should be called at any time after driver was initialized and there are no ongoing conversions.

When you suspend debug session, in Expressions tab you can observe results: g_fifo1Result, which corresponds to the BCTU list measurements, meanwhile g_fifo1Volts corresponds to the conversion in volts.

We hope this resolves your issue.

For more questions, please help me creating a new post.