- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

In my design, I need to sample two ADC channels simultaneously by doing the ADC parallel conversion. The sampling time for a single ADC channel is about 1.34 µs.

What is the right way to do it? My understanding so far:

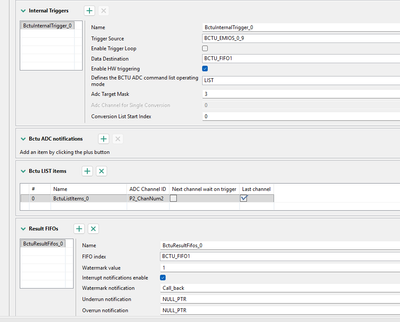

When configuring the BCTU (see the image below), the expectation is that it will initiate conversions on both ADC0 and ADC1 simultaneously. Based on my understanding of cross-triggering and parallel conversion:

- The FIFO should receive two results:

ADC0_CH2 and ADC1_CH2,

both sampled within the same 1.34 µs time window.

Is this understanding correct?

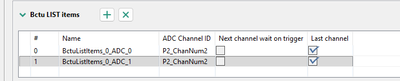

From my testing (Se the image below ), it appears that the BCTU list determines the order of conversions, where:

- First entry → ADC0

- Second entry → ADC1

The FIFO then receives two results:

- ADC0_CH2

- ADC1_CH5

This raises an important question:

Does true parallel sampling occur, or are these conversions still sequential?

If they are sequential, what is the actual timing?

Is it still 1.34 µs per signal, or does the system complete both within the same 1.34 µs window?

In addition to my previous observations, I have more question:

What Are the Downsides of Parallel ADC Conversion?

What happens when we configure the system to sample the same channel on two different ADC instances (ADC0 and ADC1) at the same time?

- Does this introduce extra noise due to simultaneous sampling on the same signal line?

- Is there any delay or timing penalty compared to sampling different channels?

Which Approach Do You Recommend?

- Sampling the same channel simultaneously on two different ADCs, or

- Sampling two different channels simultaneously on two different ADCs?

I hope to get a clear answer to all these questions because understanding these details is crucial for designing an efficient and reliable system.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi@Ayaz

Since ADC0 and ADC1 are sampled in parallel, the functions achieved by these two methods are the same. In my opinion, there is no difference.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi@Ayaz

Some of your settings are incorrect, but you might be getting correct results, which may be a bit confusing.

I'll summarize your answer below:

The FIFO should receive two results:ADC0_CH2 and ADC1_CH2,both sampled within the same 1.34 µs time window.Is this understanding correct?

This is not correct. The result you get from the test should be ADC0-CH2 & ADC1-CH0.

You may have some doubts, but please don't delve into it too deeply, because this is a wrong setting in itself.

Also , for your this configuration:

You can get the correct result, but I don't recommend it, as it can easily lead to misunderstandings.

Which Approach Do You Recommend?

- Sampling the same channel simultaneously on two different ADCs,

- Sampling two different channels simultaneously on two different ADCs?

for example:

ADC0-CH2 & ADC1-CH2 will parallel conversions

ADC0-CH2 & ADC1-CH5 will parallel conversions

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for the information.

Could you please explain more clearly why this approach is not recommended?

I’ve followed the instructions provided in an NXP knowledge-sharing article, so I’d like to understand the reasoning behind the concerns.

Also, regarding ADC sampling:

Can you elaborate on the implications of these two scenarios?

Sampling two different ADC channels simultaneously on two different ADCs.

Sampling the same ADC channel using two different ADCs.

What are the key differences between these two methods?

Does this introduce extra noise due to simultaneous sampling on the same signal line?Is there any delay or timing penalty compared to sampling different channels?Could this affect accuracy?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi@Ayaz

Can you elaborate on the implications of these two scenarios?

Sampling two different ADC channels simultaneously on two different ADCs.

Sampling the same ADC channel using two different ADCs.

What are the key differences between these two methods?

---------------------------------------------------------------------------------

In fact, these two situations are exactly the same, there is no difference. ADC0-CH0 and ADC1-CH0 are not the same channel, which you need to understand.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

Thanks for your information

When configuring the BCTU for parallel conversions across two ADC instances (ADC0 and ADC1), where:

- ADC0 includes channels CH1, CH2, CH3

- ADC1 includes channels CH4, CH5, CH6

Should the BCTU configuration define the “last channel” based on the following scenarios:

- The final channel in the combined sequence (e.g., CH6),

Or - The last channel for each ADC instance individually (e.g., CH3 for ADC0 and CH6 for ADC1)?

Your previous snapshots show that only one last channel needs to be enabled/ticked (scenario 1), whereas this post: Example S32K344 PIT BTCU parallel ADC FIFO DMA DS3.5 RTD300 - NXP Community suggests that last channel should be enabled/ticked for both the channels of ADC0 and ADC1 (scenario 2).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi@Ayaz

Since ADC0 and ADC1 are sampled in parallel, the functions achieved by these two methods are the same. In my opinion, there is no difference.