- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hello Community,

S32k144 part number : FS32K144HAT0MLLT

I am facing issue with the ADC conversion.

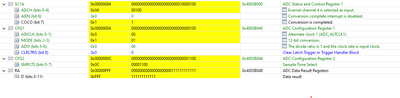

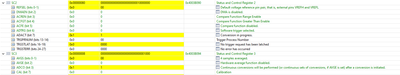

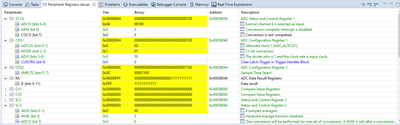

My bus clock (48Mhz) and ADC clock (24MHz) with 12 bit resolution and 12 sample time.

Vin= 0 to 3.3v.

I am got the ADC output for my Vin (0 to 3.3). I only get results 0 or 4095. I'm not getting a linear output. Instead, I'm getting low(0) and high(4095) values . How to solve this problem.

Thanks in advance,

Sarwath

已解决! 转到解答。

Hello @sarwath,

Can you scope the Vin signal during the conversion?

Do you use the correct channel?

Please double check the VREFH reference.

Have you tried using a longer sample time or slower ADC clock?

Thanks,

BR, Daniel

One way to reduce ADC errors is to augment the design by using larger analog components. This approach improves matching, and therefore distortion numbers, but requires more area and power.

Regards,

Rachel Gomez

Hello @sarwath,

Can you scope the Vin signal during the conversion?

Do you use the correct channel?

Please double check the VREFH reference.

Have you tried using a longer sample time or slower ADC clock?

Thanks,

BR, Daniel

Hello @danielmartynek ,

I am using FIRC as my system source clock and SPLL , SOSC are disabled.

Yes I verified the Vin signal during the conversion. It is constant 1.5v

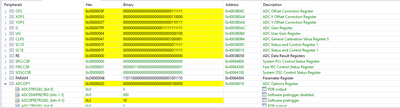

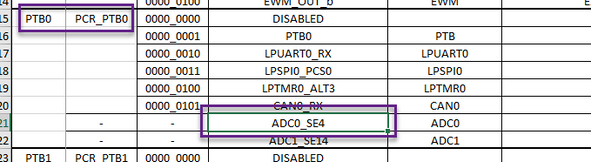

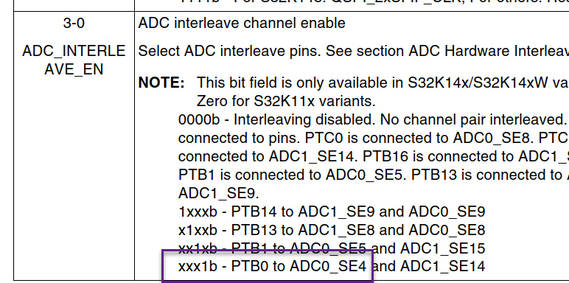

I am using channel ADC0_SE4.

VREFH =3.3v.

I gave longer sample time =250 and slower ADC clock =24Mhz and I am still getting the output RA as 0 or 4095.

I have attached my register values below,

B.R,

Sarwath