- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32G

- :

- When is SSRAM accessible before s32_ssram_clear?

When is SSRAM accessible before s32_ssram_clear?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

Which reset reason is SSRAM accessible before s32_ssram_clear function?

Best regards,

Jeff Huang

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Jeff-CF-Huang,

Thanks for the clarification, I did understand the question differently.

To know when exactly the SSRAM content is retained please check the section 28.7 Chip status on reset exit of the Reference manual [page 1150, S32G2 Reference Manual, Rev. 8, February 2024]:

Please check the reference manual for full information.

In the table I mentioned before you can see the resets that are of type functional:

About the status of the SSRAM you can check the 35.3.5 Platform RAM Status Register (PRAMSR) register to know if it was successfully initialized and therefore can be accessed [page 1436, S32G2 Reference Manual, Rev. 8, February 2024]:

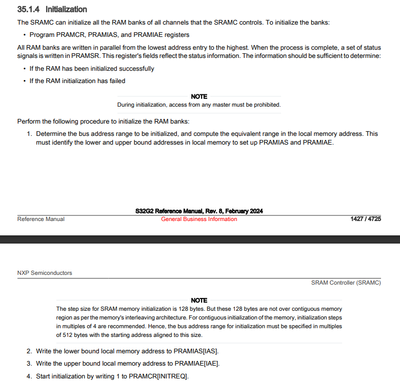

You can learn more about how to initialize the SSRAM in section 35.1.4 Initialization, under Chapter 35 SRAM Controller (SRAMC) [page 1427, S32G2 Reference Manual, Rev. 8, February 2024]:

My understanding is that with a functional reset (this is when the information is retained) the SSRAM should not loose the initialization status and therefore you should be able to read it without problems. Please note that the SSRAM depends on the STANDBY power domain (VDD_IO_STBY), so that voltage needs to be kept in order to retain the SSRAM data.

I used the S32G2 RM as reference since I do not know which component you are using.

Let me know if this information solved your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Jeff-CF-Huang,

Checking the reference manual for the registers value for reset (MC_RGM_DES and MC_RGM_DES) which are read in function static enum reset_cause get_reset_cause(void) [.../arm-trusted-firmware/plat/nxp/s32/s32cc/s32g/s32g_bl2_el3.c][page 1139, S32G2 Reference Manual, Rev. 8, February 2024] (please check the full table in the document for better reference):

I was not able to find any error directly related to the a SSRAM access. Please provide the following information to have better context of your setup:

- Have you experienced problems when accessing the SSRAM before clearing it?

- Are you using a S32G2 or S32G3?

- Which version of the BSP are you using?

- Are you using a multicore setup? this is M7 and A53 cores

- which boot type are you using? QSPI, SD, eMMC, serial

- Are you using a custom board or a RDB board?

- Are you using the GCC version indicated in your BSP user manual?

Thanks for the information in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alejandro,

It seems there’s a misunderstanding.

The s32_ssram_clear function initializes and clears the SSRAM in BL2 of ATF.

If we want to retrieve data from SSRAM after an XXX reboot, we need to access SSRAM before this function is called.

However, we are unsure which type of reboot allows SSRAM to be safely read.

From what we know, reading SSRAM before s32_ssram_clear during a POR scenario results in a system fault.

Best regards,

Jeff Huang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @Jeff-CF-Huang,

Thanks for the clarification, I did understand the question differently.

To know when exactly the SSRAM content is retained please check the section 28.7 Chip status on reset exit of the Reference manual [page 1150, S32G2 Reference Manual, Rev. 8, February 2024]:

Please check the reference manual for full information.

In the table I mentioned before you can see the resets that are of type functional:

About the status of the SSRAM you can check the 35.3.5 Platform RAM Status Register (PRAMSR) register to know if it was successfully initialized and therefore can be accessed [page 1436, S32G2 Reference Manual, Rev. 8, February 2024]:

You can learn more about how to initialize the SSRAM in section 35.1.4 Initialization, under Chapter 35 SRAM Controller (SRAMC) [page 1427, S32G2 Reference Manual, Rev. 8, February 2024]:

My understanding is that with a functional reset (this is when the information is retained) the SSRAM should not loose the initialization status and therefore you should be able to read it without problems. Please note that the SSRAM depends on the STANDBY power domain (VDD_IO_STBY), so that voltage needs to be kept in order to retain the SSRAM data.

I used the S32G2 RM as reference since I do not know which component you are using.

Let me know if this information solved your question.