- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32G

- :

- CAN issue multicore

CAN issue multicore

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CAN issue multicore

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using s32g3 board.

A core- BSP42

M core - Autosar.

When we boot M core alone, the messages are being transmitted at 500 baud rate.

When we boot both m core and A core simultaneously , after the A core boots, the m core stops transmitting messages at 500 baud rate. The baud rate gets reduced to 296 automatically and the messages starts getting transmitted at 296 baud rate.

We are suspecting that the issue is with clock.

Can you let us know how to proceed and solve the issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Abhiram_m_s,

If you are not going to use CAN with linux the first approach you should try is to comment the can nodes at the device tree.

You will see there is from can0 to can3 in the file s32cc.dtsi at the linux repository.

Comment these nodes, compile it and upload the new device tree to your board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

We are using flexcan on A core side and LLCE can on M core side.

we cannot remove CAN from A core as it is important.

Is there any other way we can solve thise?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Abhiram_m_s,

Which version of LLCE are you using?

Are you using IPCF?

Your configuration of the flexcan at the A core is to transmit at the same baudrate? If not, why not?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @carlos_o ,

We are using LLCE 1.0.9 in M core.

We are using IPCF 4.10 but will that cause an issue?

A core is also transmitting the messages at 500k itself.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Abhiram_m_s,

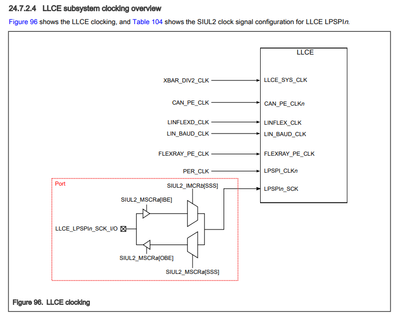

You need to review your clocking configurations from the LLCE side at your M7 core.

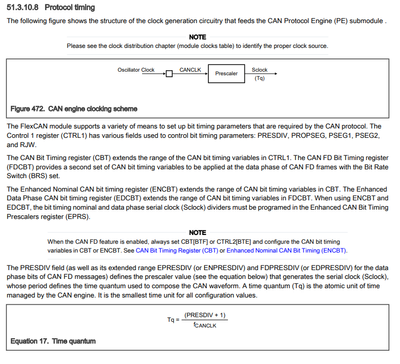

[page 2768, S32G3 Reference Manual, Rev. 4, 02/2024]

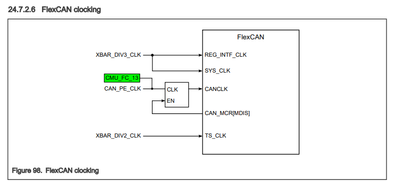

For FlexCAN with the A53 Core review the following:

[page 2619, S32G3 Reference Manual, Rev. 4, 02/2024]

Reviewing the Clocking chapter of the RM.

[page 921, S32G3 Reference Manual, Rev. 4, 02/2024]

[page 918, S32G3 Reference Manual, Rev. 4, 02/2024]

As you can see LLCE and FlexCAN shares the Clock for transmit you need to review your configuration of each module to use the same prescaler to match the frequencies in both transmit options.

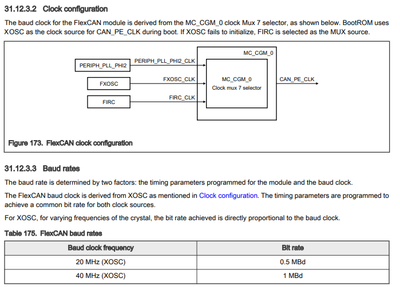

Some other important information to know here is where this clock is generated:

[page 1346, S32G3 Reference Manual, Rev. 4, 02/2024]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @carlos_o ,

Where can we change the clock source in A core side.

Can you give me the detailed procedure.

I checked in device tree script, it is not there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Abhiram_m_s,

The clocks can be modified at the ATF side, but for the problem you are presenting there can be a multiple reason of it.

The first is to verify which clock is selecting the CGM_MUX_7 when you start the M7 and if this is the same or change when you start the A53 Core.

Could you please share the configuration of the M7 side of the CAN_PE_CLK and the CGM_MUX_7? If CGM_MUX_7 is selecting the PLL_PH2 please share the values of it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The m core configuration is here below

Please let us know how to go ahead.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Abhiram_m_s,

Thanks for sharing your configuration of the CAN CLK in the M7 core.

Can you run the following commands in linux after boot?

devmem2 0x400304c0

devmem2 0x4003c008

devmem2 0x4003c08c

devmem2 0x401b4004

devmem2 0x401be004

devmem2 0x402a8004

devmem2 0x402b2004

This command is mapping registers to user space, I want to see how the kernel is configuring the FlexCAN registers and the PLL & CGM registers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Carlos

I ran the commands given by you and the output is as follows

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Abhiram_m_s,

Thanks for sharing the output of the registers.

It seems that the clock that LLCE and FlexCAN use is not being modified by the kernel configuration.

Did you run these commands right next to power up the A53 core? if yes, can you run it again after configuring the CAN transmit in the A53?

Also, can you share how are you configuring the A53 to use FlexCAN?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @carlos_o

Sorry for delay in response

Did you run these commands right next to power up the A53 core? if yes, can you run it again after configuring the CAN transmit in the A53?

Ans : I did run it after power up and after can transmit, there was no notable change.

I am attaching my Mcore side can configurations

Baud rate configurations are attached below :

The MCU clock reference point is below:

Below is the bootloader side configuration :

can you share how are you configuring the A53 to use FlexCAN?

ans : All clock configurations is handled in Bootloader, there is no clock configuration in Acore.

I will attach the screenshot of the Devicetree below

Please check and let us know the issue.