- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

I am setting the SPI with S32DS configure tool, when I select the Transfer type DMA, and the Callback function is the SPI sent complete or the EDMA sent complete callback?? if this is the SPI transfer complete callback, Where to set the EDMA transfer complete callback? anybody know are there any doc for reference? I am confuse, Thanks

已解决! 转到解答。

Yes, that would be much more effective.

If the TX FIFO is written before the LPSPI module shifts the last word, there will be no gap between the frames.

BR, Daniel

Hello @linton,

You did not specify the MCU and the SDK version.

But this is a callback of the LPSPI driver.

The documentation of the driver can be accessed from the IDE

Right-click on the driver -> Documentation.

Regards,

Daniel

There is no other documentation for the drivers.

What issues fo you have with the callback?

The LPSPI driver should call the callback at the end of the transfer.

There is this SPI event defined in callbacks.h

Regards,

Daniel

Hi daniel,

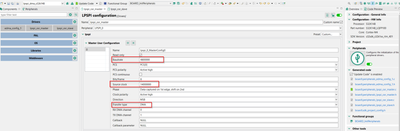

I set the LPSPI_0 as below photo show:

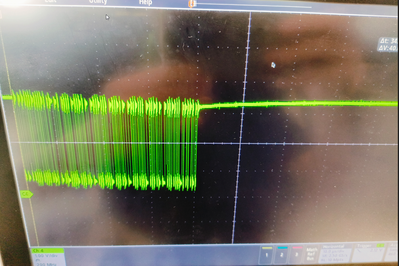

and I use the scope to test the SOUT waveform as below show:

I send 20 bytes data, so I can calculate the baudrate is about 4.2M(what I set is 4.8M), and I check the clock is right. as below show:

what cause this problem? what I need is 4.8M , 4.75 to 4.85 is acceptable. but 4.2M is bad.

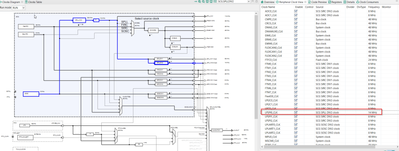

the second problem is I change the transfer type from DMA to interrupt. the configure as below:

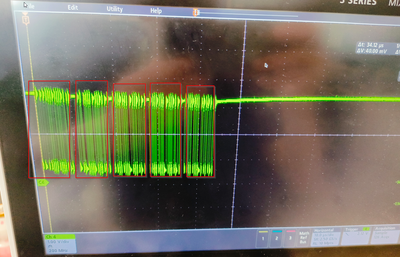

and I also use the scope to test the SOUT waveform as below show:

as you can see it separate my 20bytes data to five part, 4 bytes per part. What cause this problem?

Hi @linton,

The baudrate is calculated by the RTD driver from the LPSPI clock.

RM, 51.3.1.12 Clock Configuration Register (CCR).

Can you try using a higher freq. LPSPI clock?

It is expected to see some overhead when the interrupt mode is used, the LPSPI module has 4-word TX FIFO.

Regards,

Daniel

Hi Daniel,

now I use the higher freq(56MHZ) as below show:

but the performance did not looks better than before, it still separate to five parts(4bytes per part):

the blue is using interrupt, the green is using DMA.

are there any solution to solve this issue when I use the interrupt mode??

my application is simple as below show:

Hello @linton,

This is simply a limitation of the driver.

In general, the SDK drivers are big and cause some CPU overhead.

Enabling the cache could somewhat help but not much.

Regards,

Daniel