- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Software Forums

- :

- S32 SDK

- :

- I2S data transfer via DMA

I2S data transfer via DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2S data transfer via DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HW: S32K144 eval board

Hi experts,

I am using S32K144 with S32 design studio IDE. I want to transfer I2S(FlexIO) data with the help of DMA but don't know How can I configure. mainly I want to send continuous data on I2S.

I need help to implement logic for same. I go through example project of DMA but in that only transferring virtual to one buffer to another.

Please arrange a call so I can discuss for implementation help or share sample code which can transfer data via DMA over I2S.

Regards,

Mohit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mohit_Manvar,

Hope you are doing well! Please help me with more details about your desired implementation. I see that you added S32 SDK as a label, are you using SDK or RTD for drivers? Please specify the version as well.

If you are using RTD, there is a chapter on RTD_I2S_UM named 3.6.3 I2s over SAI DMA transfer which include some driver usage and configuration tips for I2S.

As for the call, I apologize for any inconveniences this may cause, but this open forum is only for messages/posts.

Best regards,

Julián

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm using RTM 4.0.3 for example projects along with S32Design studio v3.4.

I want to transfer data over DMA but don't know what to be configured exactly.

Need small helping reply.

Mohit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mohit_Manvar,

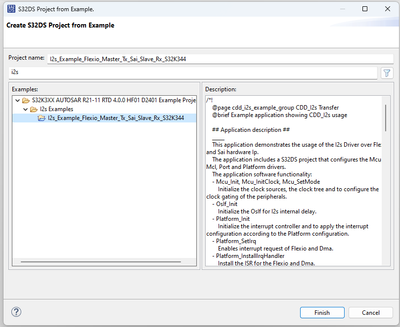

You can look into the I2S Example included in the RTD 4.0.0:

The configuration requires for the DMA module has to be initialized prior to usage in DMA mode, as well as being allocated by the application.

In interrupt mode, if mux line is enabled then user must turn on only one bit in ChannelEnable, which will be the data line to output data. Number of data buffers to be muxed is specified in ChannelCount field.

In DMA mode, if mux line is enabled then user must turn on number of bits equal to number of data buffers to be muxed. The data lines corresponding to these bits will output the same as each other.

Also in DMA mode, if a mux mode is selected, ChannelEnable must be turned on from bit 0, and immediately aboves (for example turning on bit 0 and bit 2 is not a correct configuration).

You can find some pointers for I2S FlexIO DMA transfer in this community post: S32K3 S32DS3.5 I2S demo by FlexIO with DMA - NXP Community

Best regards,

Julián

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

As I already mentioned that I'm not using RTD. I'm using RTM so I have limited options of examples.

also in parallel can you check for bare-metal code to transmit data via I2S over DMA?

I already gone through following examples but didn't find anything helpful.

Mohit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mohit_Manvar,

I apologize for the misunderstanding. Using RTM you can look inside the Design Studio folder path:

C:\NXP\S32DS.3.4\S32DS\software\S32SDK_S32K1XX_RTM_4.0.3\doc

You can look into chapter 16.53 FlexIO I2S Driver where some important notes are explained.

"This driver needs two DMA channels for its operation when it is initialized in DMA mode. The DMA channels must be initialized by the application before initializing the driver. Refer to EDMA driver for DMA channels initialization."

Please look into the document for more notes and pointers to implement the DMA and both Master/Slave for the I2S driver.

You can also take the flexio_i2s_master/slave examples from the RTM:

You can refer to the EDMA driver for DMA channel initializations.

Best regards,

Julián

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Somehow I figured out use of DMA in RTM. currently I'm facing issue of phase drift like two waveforms should be phase aligned.

I'm using FlexIo I2S for SCLk and LRCK and flexio's time and shifters (not FTM) to generate MCLK. but MCLK is not aligning with LRCK.below are some requirement and snapshots.

Requirement of waveform alignment:

Current waveforms generated:

(we are facing 10ns delay in clocks)

we need solution to generate all clocks on same time and it should generate continuous once we enable them.

Regards,

Mohit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Mohit_Manvar,

Could you share your configuration for I2S timers and shifters?

You can use as reference the following application note for communication emulation and timing peripherals using FlexIO: AN12174: Using FlexIO to emulate communications and timing peripherals.

Section 7 describes how to emulate I2S bus Master, as well as some configurations for shifters and timers.

Best regards,

Julián.