- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Software Forums

- :

- S32 Design Studio

- :

- Re: MPC5748G Bootloader Configuration (DEVKIT-MPC5748G)

MPC5748G Bootloader Configuration (DEVKIT-MPC5748G)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am working on creating a bootloader application for the MPC5748G devkit board, and I am using the S32 IDE. The requirements are as below:

- The bootloader, on bootup will check a flash location for a word indicating whether a new firmware is available or not (This word is written by the main firmware on receiving a new firmware and saving it to flash).

- If available, it will copy the new firmware and replace it with the old firmware(user application).

- If unavailable, bootloader will boot the current firmware.

- The firmware update process takes place via ETHERNET from the user application, not serial interface.

I have downloaded the Bootloader_MPC5748G bootloader code from the Example codes, but need some help as I am working on bootloader for the first time, and the schedule is tight. I have modified the linker scripts of the user application and the bootloader.

The main question I have is how to jump to the user application from the bootloader after checking the word.

It would be very helpful if you could provide some insight into this. I want to do the jump from the main function itself, and I was unable to find any info in the bootloader application regarding this. I have attached the bootloader code here.

The bootloader's linker script is:

Bootloader

SRAM_SIZE = 128K;

SRAM_BASE_ADDR = 0x40000000;

MEMORY

{

flash_rchw : org = 0x00F8C000, len = 16K

m_text : org = 0x1000000, len = 256K

m_data : org = 0x40000000, len = 128K

}

The user application's linker scripts are as follows:

Core 0

SRAM_SIZE = 256K;

SRAM_BASE_ADDR = 0x40020000;

MEMORY

{

flash_rchw : org = 0x00FA0000, len = 0x4

cpu0_reset_vec : org = 0x00FA0000+0x10, len = 0x4

cpu1_reset_vec : org = 0x00FA0000+0x14, len = 0x4

cpu2_reset_vec : org = 0x00FA0000+0x04, len = 0x4

m_text : org = 0x1040000, len = 1856K

m_data : org = 0x40020000, len = 256K

}

Core 1

SRAM_SIZE = 256K;

SRAM_BASE_ADDR = 0x40060000;

MEMORY

{

flash_rchw : org = 0x00FA0000, len = 0x4

cpu0_reset_vec : org = 0x00FA0000+0x10, len = 0x4

cpu1_reset_vec : org = 0x00FA0000+0x14, len = 0x4

cpu2_reset_vec : org = 0x00FA0000+0x04, len = 0x4

m_text : org = 0x1210000, len = 1856K

m_data : org = 0x40060000, len = 256K

}

core 2

SRAM_SIZE = 128K;

/* Define SRAM Base Address */

SRAM_BASE_ADDR = 0x400A0000;

MEMORY

{

flash_rchw : org = 0x00FA0000, len = 0x4

cpu0_reset_vec : org = 0x00FA0000+0x10, len = 0x4

cpu1_reset_vec : org = 0x00FA0000+0x14, len = 0x4

cpu2_reset_vec : org = 0x00FA0000+0x04, len = 0x4

m_text : org = 0x13E0000, len = 1600K

m_data : org = 0x400A0000, len = 128K

}

Any help would be greatly appreciated.

stanish uditsalunke lukaszadrapa martinkovar gigi3

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can use assembly branch instruction to application's main function - e_bl .

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Navinar,

I am developing a can-based bootloader. May I ask if you can share your bootloader code for my reference? Thank you very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 1642280511@qq.com,

I am looking for can-based bootloader,but I can not work it well still, Could you share can-base bootloader code for me ?Thanks very much. My email is 78329668@qq.com

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So user application is responsible for downloading NEW user application

(over Ethernet) and update the flash word as flag for boot loader. May be

user application can do Soft Reset to get boot loader in action.

I think starting NEW application is simple - just jump to the start

address.

The critical part here is to execute boot loader when its performing flash

operation ie. erase and write.

Where is validity check for NEW application is done?

Udit

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Udit,

Thanks for the prompt reply. I have not yet implemented the ethernet feature to update the firmware. Right now, I am working on implementing the bootloader functionality - i.e., the bootloader will bootup and jump to the firmware which I have already flashed as per the linker script given above.

Once the firmware update feature is in place, I will indeed write the word to flash and do a software reset so the bootloader can replace the new firmware and boot from it.

I need to know how to do the jump to the firmware address from the bootloader. In this case, the firmware's boot header is at 0x00FA0000, so how do I initiate the jump from the main function?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can use assembly branch instruction to application's main function - e_bl .

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

I used the following instructions to jump to the user app (Got them from another forum post).

asm("e_lis %r12,0x0104");

asm("e_or2i %r12,0x0000");

asm("mtlr %r12");

asm("se_blrl");

Thanks for you help!!!

Best Regards,

Navinar Savad

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Navinar

you use this method as follow is OK?

asm("e_lis %r12,0x0104");

asm("e_or2i %r12,0x0000");

asm("mtlr %r12");

asm("se_blrl");

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi chengxueyuan0210@163.com, I used the following function in the bootloader application to jump to my user application.

void jump_to_user_app(void)

{

//Jump to upgraded fw or golden image.

asm("e_lis %r12,0x012C");

asm("e_or2i %r12,0x0000");

asm("mtlr %r12");

asm("se_blrl");

}

The user application should be flashed to the address 0x012C0000. I am including it's linker script below - "57xx_flash.ld" (Please note that I only used one core in the MPC5748G controller). The location of this linker script is $user_application_project/Project_Settings/Linker_Files.

Best Regards,

Navinar Savad

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

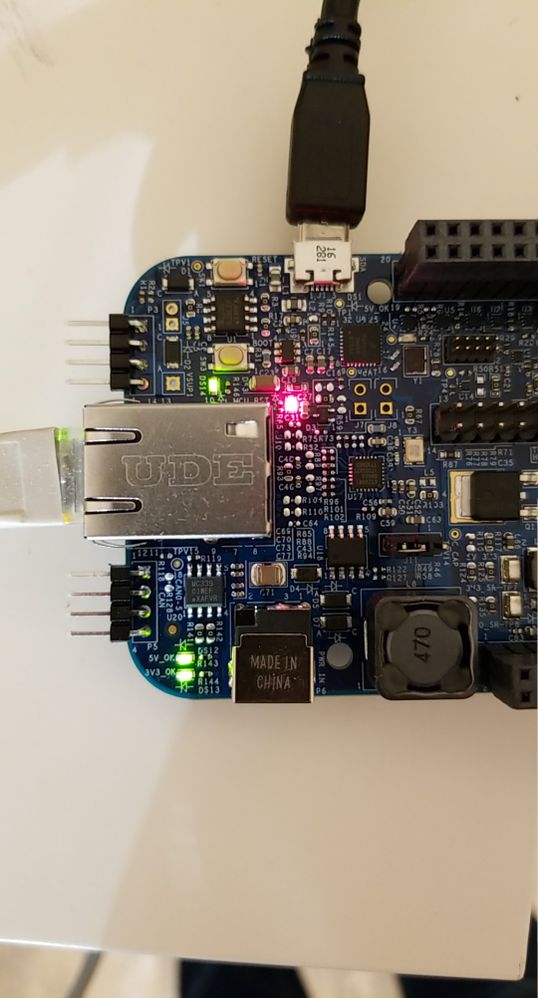

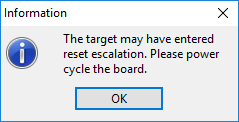

Thanks for replying. I was in fact trying to do the same but ran into reset escalation issue. Trying to get the board working again.

;if the boot header is valid, execute application

;load address of reset vector to r12

e_lis r12,0x00FA

e_or2i r12,0x0010

;load reset vector to r0

e_lwz r0,0(r12)

;move reset vector to link register

mtlr r0

;branch to address in link register

se_blrl

I was going to run the assembler code given above. I got it from the Bootloader code for Greenhills ide. Do you think this is sufficient? I will be able to test only once the board works. It is in a reset state now. Do you have any solution to this issue? I have been trying out the solutions listed in a couple of the forum posts but none of them works. I was using the OpenSDA debugger, but once this issue manifested, tried with the P&E Universal debugger also. Still the same.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

actually - instead of reset vector address you should use the application's main function address.

Here is similar thread related to bootloader - for S32K144, but the principle is same:

https://community.nxp.com/message/964316

Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the update.

I had seen that post before and tried to do that call, but using the reset vector address.

//__asm__("b 0x00FA0000");

But it was not working. I will use the main function's address and try again if I can get the board to work.

Do you have a solution to the reset escalation issue? I am running out of ideas and would greatly appreciate some help.

Navinar

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Navinar,

I think instead of jumping to boot header of user application, branch to applications entry function.

Boot headers are used by BAF to start an application. I am not sure that can be done from user application.

also you can check what type of reset is escalated?

Udit