- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- QorIQ

- :

- Re: LS1043A Event Processor EVT Pin Control Register

LS1043A Event Processor EVT Pin Control Register

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

On LS1043A, we are trying to set the DIR bits of the Event Processor EVT Pin Control Register (EPEVTCR0) 0 to 9.

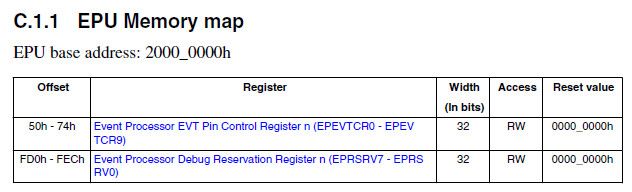

Based on LS1043a Reference manual Rev 6, these registers are in the DCSR region with EPU base address=0x60000 and offset 0x50 for EPEVTCR0. So the full address should be 0x20060050. But writing to this register and reading back always return's 0. We tried to do this with PBI commands and u-boot without success.

Also, there was an update in revision 6 of the LS1043A Reference Manual, where they say DCSR_BASE to be 0x07 0000 0000. Based on Table 2-1. System memory map, I believe this address is for another LS version, but would like confirmation. Appendix C of the Reference Manual also state: "All registers are accessible with 32-bit accesses. The EPU registers are configurable via DCSR."

Regards,

Frank

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Following your reply I had to take few steps back.

The register is Big Endian but the RCW/PBI compiler seems to handle this. So the code I have provided above does work. The tool I was using to read back the values in Linux the problem.

Best regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Correct memory map for the EPU is:

The QorIQ LS1043A Reference Manual will be fixed in the next revision.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for your reply.

So the information in Reference Manual Rev 5 were ok, and we should be able to access EPEVTCR0 register at address 0x20000050.

But then we still have a problem. Our original SW was programming this register with value 0x00000001 with PBI commands as follow:

//.pbi

// Setting EPU module, Base address 0x20000000

write 0x570158, 0x00002000

// Software must wait after updating the ALTCBAR.

// Below is the PBL Wait command (0xc0)

write 0x6100c0, 0x000fffff

awrite 0x000050, 0x00000001 // EVT0

awrite 0x000054, 0x00000001 // EVT1

awrite 0x000058, 0x00000001 // EVT2

awrite 0x00005C, 0x00000001 // EVT3

awrite 0x000060, 0x00000001 // EVT4

awrite 0x000074, 0x00000001 // EVT9

.end

But when we try to read back these registers in u-boot or Linux, their value are still 0. Is there a way to confirm that the write was properly handled ?

Regards,

Frank

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It could be an endian issue - please try:

awrite 0x000050, 0x01000000 // EVT0

....

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Following your reply I had to take few steps back.

The register is Big Endian but the RCW/PBI compiler seems to handle this. So the code I have provided above does work. The tool I was using to read back the values in Linux the problem.

Best regards