- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Inter byte SPI delay

Inter byte SPI delay

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Inter byte SPI delay

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

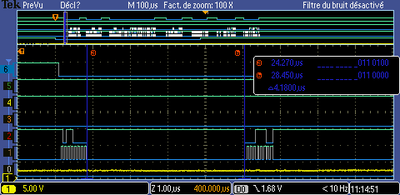

I have a custom board with LS1028A and a MCP2518FD CAN controller on SPI1 bus. All works fine but when we take a look at SPI bus, we see that performance are not maximum.

A SPI transfer is composed as following : many bytes are send and during all this time, CS is asserted. After, CS is released during a period (about 20us) and at the end of this time, another transfer begins with many byte send (always with CS tied low during transfer). This sequence is repeated 4/5 times.

We observe that :

- there are long inter byte delay (about 4us). A SPI byte takes about 0,7us.

- there are long inter frame delay (about 20us). It corresponds to desasserted time of CS between 2 frames.

Settings of Tasc and Tcsc are good, and are correctly defied in device tree.

If I understand datasheet, asserted CS during many bytes transfer correspond to continous mode operation. In this case inter byte delay shoud be sum of Tasc and Tcsc, but it is not true here.

We tried to set PDT and DT to reduce CS desasserted time without success.

We tried to activate fast continuous mode to supress Tasc and Tcsc between byte without success.

We didn't understand why all our registers modification haven't effect on SPI timing, and why we have these timings.

Has anybody have already this problem ? how to fix it ?

Regards

Jeremy

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jbonhomme,

Did you finally solved your inter byte delay problem?

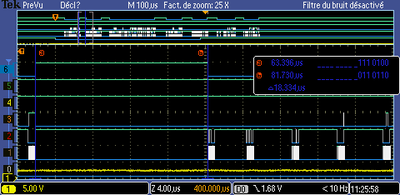

We're working with a LS1046A and notice similar behaviour during SPI transfers: 2µs delay between consecutive bytes (and 11µs between deassertion and reassertion of CS). We would like to reduce as much as possible the inter byte delay.

@Pavel / @NXP: Is there any driver improvement planned in the coming future?

Any suggestion is welcome.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Linux BSP dSPI driver was not optimized for performance.

Check the CTARx[DT] value.

Check the CTAREx[DTCP] value.

Send multiple data frames using a single command frame. See the Section 30.5 in the LS1028a Reference Manual.

https://www.nxp.com/webapp/Download?colCode=LS1028ARM

See also the Section 30.6.