- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- Boot the DSP multiple times without using target reset.

Boot the DSP multiple times without using target reset.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Boot the DSP multiple times without using target reset.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Is there anyway to be able to re-run the program multiple times (on the DSP) without using 'tgreset' command?

On the first trial, 'dsp boot' dumps the following output:

Het Mgr 248 0

IPC: dsp_shared_size - 0x1000000

IPC: dsp_private_addr - 0x80000000

IPC: dsp_private_size - 0x7ff00000

IPC: shared_ctrl_addr - 0xfff00000

IPC: shared_ctrl_size - 0x100000

IPC: max_num_ipc_channels 64

IPC: max_channel_depth 16

fsl_shm module installed successfully withmajor num : 247

fsl_l1d Major=246 Minor=0

===B4860QDS DSP boot Application (3.0.0) ===

SYSTEM MAP

DSP PrivArea: Addr=80000000 Size=7ff00000

Shared CtrlArea: Addr=fff00000 Size=100000

DSP Core0 M2: Addr=0 Size=0

DSP Core1 M2: Addr=0 Size=0

DSP M3: Addr=c40000000 Size=8000

PA CCSRBAR: Addr =ffe000000 Size=1000000

DSP CCSRBAR: Addr =ffe000000 Size=1000000

DBG: Addr =0 Size=0

PA Shared Area: Addr=60000000 Size=f000000

DSP Shared Area: Addr=6f000000 Size=1000000

PA Debug Print Shared Area: Addr=0 Size=0

DSP Debug Print Shared Area: Addr=c40000000 Size=8000

Loading Dsp image eNBL1.bin

Copy Part 80000000 2c1bc(repeated copying commands)

Copy Part a40b4000 32c42

intvec_addr =a405e000 in L1 Binary

Before StarCore release ========

LCC_BSTRH=0x0

LCC_BSTRL=0x7ffff000

LCC_BSTAR=0x8110000b

GCR_CDCER0=0x0

GCR_CHMER0=0x0

DCFG_BRR=0xf

After StarCore release ========

LCC_BSTRH=0x0

LCC_BSTRL=0xa405e000

LCC_BSTAR=0x8100000c

GCR_CDCER0=0x3f0

GCR_CHMER0=0x3f00

DCFG_BRR=0x3ff

BSTRL,BSTAR,CDCERO,CHMERO n DCFG_BRR set now

sleep 1, waiting for hw sem

sleep 1, waiting for hw sem

HS_MPR[1]=0xfe

HS_MPR[1]=0x0

== DSP Booted up ==

The next time I run 'dsp boot' without 'tgreset', I get the following output:

Het Mgr 248 0

IPC: dsp_shared_size - 0x1000000

IPC: dsp_private_addr - 0x80000000

IPC: dsp_private_size - 0x7ff00000

IPC: shared_ctrl_addr - 0xfff00000

IPC: shared_ctrl_size - 0x100000

IPC: max_num_ipc_channels 64

IPC: max_channel_depth 16

fsl_shm module installed successfully withmajor num : 247

fsl_l1d Major=246 Minor=0

===B4860QDS DSP boot Application (3.0.0) ===

SYSTEM MAP

DSP PrivArea: Addr=80000000 Size=7ff00000

Shared CtrlArea: Addr=fff00000 Size=100000

DSP Core0 M2: Addr=0 Size=0

DSP Core1 M2: Addr=0 Size=0

DSP M3: Addr=c40000000 Size=8000

PA CCSRBAR: Addr =ffe000000 Size=1000000

DSP CCSRBAR: Addr =ffe000000 Size=1000000

DBG: Addr =0 Size=0

PA Shared Area: Addr=60000000 Size=f000000

DSP Shared Area: Addr=6f000000 Size=1000000

PA Debug Print Shared Area: Addr=0 Size=0

DSP Debug Print Shared Area: Addr=c40000000 Size=8000

Loading Dsp image eNBL1.bin

Copy Part 80000000 2c1bc

(repeated copying commands)

Copy Part a40b4000 32c42

intvec_addr =a405e000 in L1 Binary

Before StarCore release ========

LCC_BSTRH=0x0

LCC_BSTRL=0xa405e000

LCC_BSTAR=0x8100000c

GCR_CDCER0=0x3f0

GCR_CHMER0=0x3f00

DCFG_BRR=0x3ff

After StarCore release ========

LCC_BSTRH=0x0

LCC_BSTRL=0xa405e000

LCC_BSTAR=0x8100000c

GCR_CDCER0=0x3f0

GCR_CHMER0=0x3f00

DCFG_BRR=0x3ff

BSTRL,BSTAR,CDCERO,CHMERO n DCFG_BRR set nowsleep 1, waiting for hw sem

sleep 1, waiting for hw semInfinitely repeated (sleep 1, waiting for hw sem)

Am I missing something?

Is there a way to reset the DSP without using 'tgreset'?

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

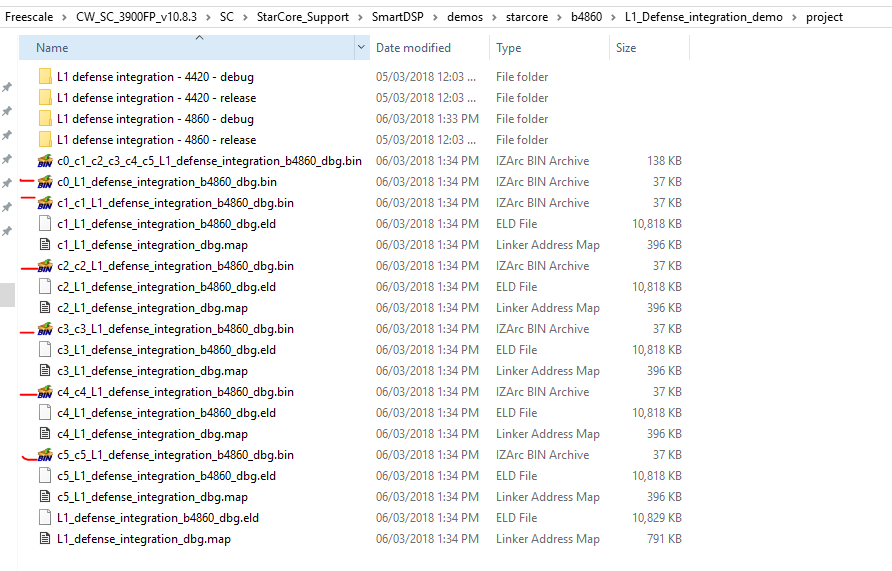

I found a demo called 'L1 Defense App' in SmartDSP demos folder. Based on what I read in README file, this app is divided into 2 parts:

- A program that runs on the PA 'l1d_app" (which requests the DSP to prepare for a reset, then waits for the DSP to respond with an ACK signal).

- The demo application (L1_Defense_integration_demo) that waits for the reset signal from PA and sends the ACK so that the reset procedure starts.

I built the project without any modifications then loaded the 6 binary images using 'dsp boot'. Below are the 6 binary images I got after the build.

But finally, I got stuck in 'sleep 1, waiting for hw sem' message in 'dsp boot'.

Any help would be appreciated!

Thanks,