- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 软件论坛

- :

- Processor Expert软件

- :

- SPI - clock polarity

SPI - clock polarity

SPI - clock polarity

Hello

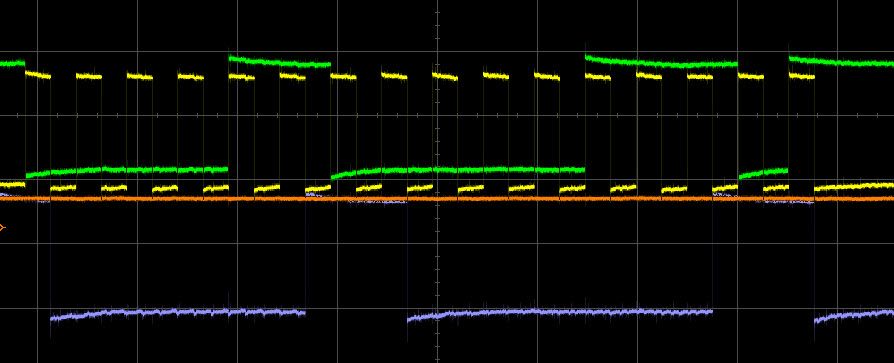

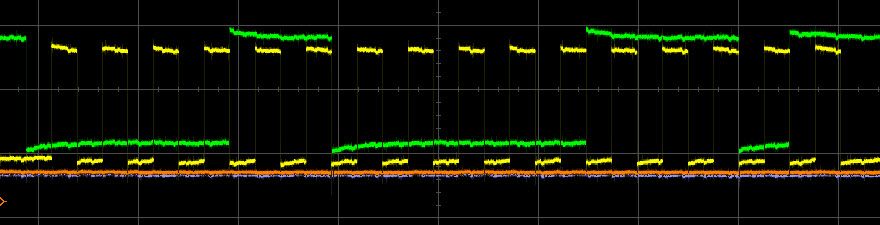

I am using DSC (56F84567) as master SPI. the slave chip read data bit on clock rising edge. However, setting the SPI clock to "rising edge" dont give any setup time to data to be stable before sending the clock, so the slave can't read the data.

When setting the clock polarity to falling edge, the clock is shifted and the slave can read the data on rising edge.

Is there a way in SPI component to set the data stabilization time by shifting the clock?

Hi, Benny,

First of all, can you tell us the signal name for the screenshot of the scope?

BTW, I see that the SPI of MC56F84567 is master, based on the SPI protocol, when the SPI is idle, the /SS pin should be high, there should not be clock signal within the high logic of /SS.

Can you tell us whether the /SS signal is generated by the SPI module itself or GPIO pin controlled by firmware?

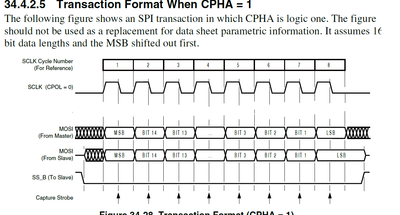

This is the SPI timing:

From above spi timing, you can see that the rising edge of SCLK triggers the data pin MOSI to be valid, falling edge of SCLK will latch the data pin on the slave SPI receiver. So the setting up time is half clock cycle time of SCLK, the holding time is the half of the SCLK cycle time.

BR

XiangJun Rong