- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 产品论坛

- :

- PowerQUICC处理器

- :

- T1023 boot problem

T1023 boot problem

T1023 boot problem

It is needed to doublecheck the processor schematics referring the QorIQ T1023, T1013 Data Sheet, Table 1. Pinout list by bus to ensure that all signals having notes are properly terminated and have correct levels during POR.

T1013 Data Sheet, Table 1. Pinout list has been set as required, but booting fails. After the PORESET goes high, the RCW value stored in the flash is being read properly.

All signals go low.

These signals are connected to nor-flash, FPGA, latch-buffer.

If the IFC_AD signal is high impedance in the FPGA while PRESET is low, these signals will go low. So, while the PRESET is low in the FPGA, some of the IFC_AD signals are made high.

If the IFC_AD signal is high impedance in the FPGA while PRESET is low, these signals will go low. So, while the PRESET is low in the FPGA, some of the IFC_AD signals are made high.

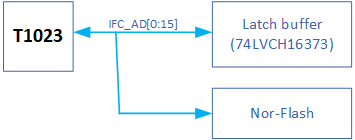

The connection is as shown. (Removed FPGA)

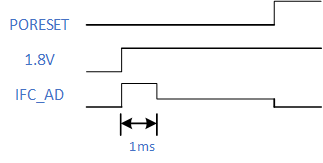

What is unusual is the initial waveform and picture of IFC_AD.

All signals work normally. (All requirements of T1023 datasheet, Table 1 are also met)

When PORESET goes high, RCW is read from nor-falsh, and when HRESET goes high, the last 8 bytes of RCW are read. After approximately 1.6 ms, ASLEEP goes low. But I can't proceed anymore here. (Sometimes it works normally.) If I go up after systemp up using Trace-32, the program works normally. Please let me know where to look.

Thank you.