- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- PowerQUICCプロセッサ

- :

- Data buffer on SDRAM path in MPC8270

Data buffer on SDRAM path in MPC8270

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Data buffer on SDRAM path in MPC8270

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

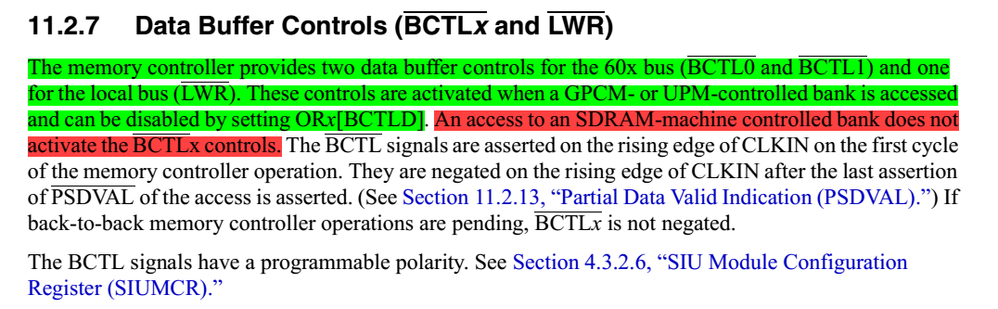

I am using 12 SDRAM's with MPC8270 and due to high capacitive load i have to add registered transceiver in the data path of SDRAM and processor. But i do not know how processor will control the direction of buffer because for flash data buffer it can control by using BCTL0 and BCTL1 but for sdram it doesnot say any thing.

Kindly tell me how can i add data buffer in data path and how to control that buffer from power PC processor .

Thanks alot

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Alexander wrote "reducing load per one data bus pin". I guess he means Chip-Select lines.

Each memory rank (32 or 64 Bit wide depending on your setting) needs to be connected to a Chip-Select line.

On a 64 Bit bus you can either connect 8 pcs SDRAM components of a x8 config, or 4 pcs of x16, or 2 pcs of x32 to each chip-select-line.

Per my knowledge the capacitive load needs to be looked at "per each chip-select". The more components you use in parallel on the same chip select, the higher the load. This being said, you should be better off by using components in x32 width on as many chip-select lines as you have available.

If you want to maximize the amount of memory your system can support, you should use memory-components with smallest possible width per SDRAM.

From your other posting I see you plan to use 512Mb SDRAM in x16, IS45S16320F-7BLA2 in BGA54 package, Automotive Grade 2 (-40 to 105°C).

If your application requires high reliability and AEC-Q100 automotive grade, take a look at the ECC SDRAM series from Intelligent Memory. They have 512 Megabit capacity SDRAM components in x8, x16 and x32, with temperature ranges Industrial (-40 to 85°C), High (-40 to 105°C) and Extreme (-40 to 125°C).

The interesting thing about the IM ECC SDRAM parts is not only that they are available in AEC-Q100 and high temperature ranges, but they have a "built-in ECC error-correction engine" which detects and corrects bit-flips automatically. The parts still are fully compatible to any other SDRAM. There is no software or hardware adaption required. The error-correction is integrated into the components and executed without requiring any activity by the CPU/controller.

Honestly speaking, most normal automotive DRAMs are just "tested to work at a certain temperature". The operation at high temperatures is achieved simply by requiring the CPU/controller to double or quadruple the refresh-rate, because the data-retention-time of DRAMs is heavily reduced at higher temperatures.

Well, yes, with shorter refresh periods you can work against the reduced data-retention at high temperature. But what most DRAM manufacturers forget is that under high operating temperatures the DRAM memory cells (capacitors) degradate much faster, which - after some time of use - can cause an exponentially increased rate of transient single-event-upsets / bit flips. These bit-flips are not "defects", but "effects". An ECC error-correction is the perfect solution to achieve a stable 24/7 operation for many years. If your design supports ECC by the CPU, you better use that. Otherwise you have the option to use IM ECC DRAM components with built-in error-correction.

To make a simple example from real life:

Laptops or PCs need to be rebooted frequently. Is it really software fails?

Servers run the same Windows software and are under much more stress, but they work stable for years and never need a reboot. Reason: Servers use ECC error-correction!

On the Intelligent Memory website I currently see the 512Mb SDRAM x8 and x16 only in TSOP, but just yesterday I talked to them and I know for sure they are now releasing the same also in BGA54 package! I guess it will be on their website soon.

The 512Mb SDRAM in x32 comes in TSOP86 or in BGA90 and is shown on the website

Part numbers

512Mb SDRAM x8 IME5108SDBETG for TSOP54 IME5108SDBETG for BGA54 (BGA should be on website soon)

512Mb SDRAM x16 IME5116SDBETG for TSOP54 IME5116SDBETG for BGA54 (BGA should be on website soon)

512Mb SDRAM x32 IME5132SDBETG for TSOP86 IME5132SDBEBG for BGA90 (BGA should be on website soon)

Regards,

Thorsten

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, BCTLx lines are not active for SDRAM. So, it looks like you can not use buffers on data bus.

I can only recommend reducing load per one data bus pin:

1. You said you are using 12 SDRAM chips, each chip has 32-bit wide data port. The data bus at the processor, however, is 64-bits, so the first recommendation is to use full 64-bit bus width, and connect SDRAM devices in pairs to create 64-bit banks. In this case you will have only 6 chips connected to each data line.

2. If this is not enough, I recommend switching to 16-bit (or even 8-bit) SDRAM devices, if possible. For 16-bit SDRAM chips you can place 4 chips in parallel to create on 64-bit memory bank, so 12 chips will create only 3 memory banks, this means you will have only 3 chips connected to each data line.

Have a great day,

Alexander

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

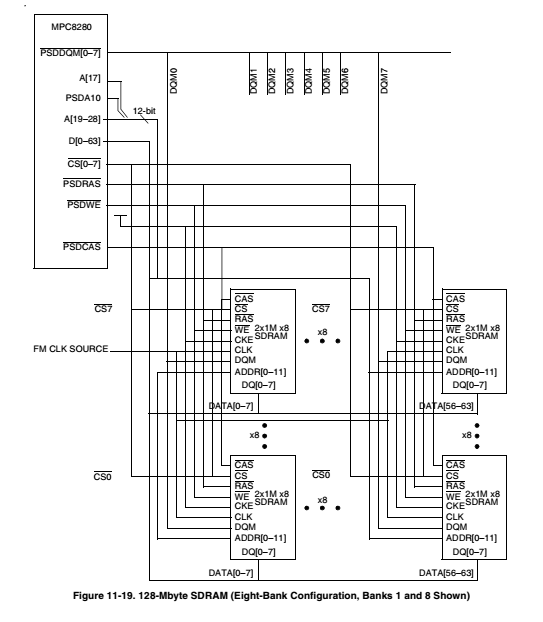

I got your point. We have this option to use 8 bit or 16 bit SDRAM devices but i do not understand how in the MPC8270 Reference manual it is shown that 64 SDRAM chips are attached to processor on 8 banks. This means data is shared on 8 lines. Considering the reference manual we do not have the control of SDRAM Data buffer so how this diagram will practically be implemented?

Fig : Pg 454 of Reference Manual 8270.

Document Pg # 11-34

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no data buffer on this figure, and the fact that 8 chips are used in parallel - does not mean data buffer should be used. The necessity of data buffer comes from total capacitance, output impedance and required speed (bus frequency).