- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Topics

- :

- NXP Designs Knowledge Base

- :

- S32G Bootloader Customzition

S32G Bootloader Customzition

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

S32G Bootloader Customzition

S32G Bootloader Customzition

This doc explain how to modify the bootloader to boot linux&mcal, to solve the conflict between bootloader, mcal and linux

本文说明在S32G2 RDB2板上如何定制开发Bootloader,本文示例主要实现功能是:

- Bootloader启动一个M核,MCAL驱动测试程序,本文分别测试了MCU,DIO,UART的MCAL驱动示例代码。

- Bootloader同时启动A53 Linux

目录

2.3 优化重排M7 demo镜像及与MPU设置的配合... 5

2.7 UART MCAL程序去掉PORT INIT. 10

2.8 UART MCAL程序修改CLOCK TREE.. 10

3.4 增加MCAL驱动所需要的PORT的初始化... 15

3.5 解决Bootloader,MCAL与Linux的clock冲突... 17

3.10 制造Bootloader的带IVT的镜像... 38

add one more doc to explain how to modify atf to boot on G3.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi John,

just curious - is this document available in english ?

Best Regards,

Viktor

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

uploaded

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Thanks a lot for the english version !

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi John,

Do you have manual for S32G3 bootloader?

Thank you a lot!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

which is the same way, just change the bootloader project version to G3.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi John

I upload the boot loader to QSPI at address 0 and fip.bin to QSPI at address 0x100000, the probe message is as follow:

NOTICE: Reset status: Power-On Reset

NOTICE: BL2: v2.5(release):bsp37.0-2.5

NOTICE: BL2: Built : 16:13:38, Nov 2 2023

Warning: Instruction at BL33_ENTRYPOINT (0xffaa0000) is 0x0, which is not a B or BL!

NOTICE: BL2: Booting BL31

Why should upload fip.bin to qspi? and the fip.bin seems can't be booted

Thank you!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi John

I also tried on S32G3EVB, the console can't probe information.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi @Johnli,

您好!

目前正在使用S32,您发布的文档对我帮助很大,非常感谢!

请教您个问题,关于A53相关的clk(core和外设),ATF、uboot、linux三部分之间是什么关系?从您的文档上看,时钟的初始化都是在ATF中,那之后的uboot和linux只是使用者吗,还是说uboot和linux也会重新配置时钟?我的理解,linux也会建立时钟树,但是linux设备树中没有看到。这部分不是很清楚,烦请您帮忙解惑。如果有相关的文档,希望您能分享下。

谢谢!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

1: 看一下时钟相关文档S32G_Supplemental_documentation_on_resolving_clock_conflicts_V1-2023.07.03.pdf。

2: linux的时钟初始化与配置,是需要传到ATF里的,所以代码在ATF中。

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi @Johnli

您好!非常感谢~

再请教您个问题。我在您分享文档中以及EB中,经常看到 "Under MCU Control",这个是什么作用?我在RM中没有找到相关描述。您能帮忙解答下吗?

谢谢!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

就是本工程mcu模块不操作此时钟的意思,在eb中可以查看一个配置项的properties

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi @Johnli

您好!

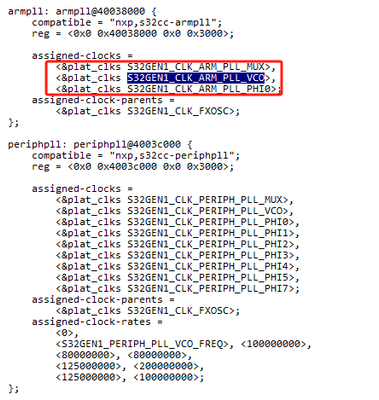

在ATF中,部分时钟为什么没有定义具体的时钟值,如下图红框中。像这种时钟,系统如何确定最终的时钟值?我跟了下ARM_PLL_VCO的相关寄存器,发现该时钟的大小和允许的最大值相同。

谢谢!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

check:

| doc&project explain the G3 bootloader customizaiton(similar with G2) to run logger demo | https://community.nxp.com/t5/NXP-Designs-Knowledge-Base/S32G-Bootloader-G3-Customization/ta-p/176952... |

| after bootloader, how to solve the clock conflict to boot ATF | https://community.nxp.com/t5/NXP-Designs-Knowledge-Base/S32G-Bootloader-Customzition/ta-p/1519838 |

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

你好,请教个问题,我使用BSP38镜像,启动之后在uboot中使用clk dump查询 llce_can_pe的时钟值,显示为0,我看了一下ATF中的设备树配置并没有发现什么问题。

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

check the doc: make sure you have load the llce driver ko.

| S32G_Bootloader_G3_LLCELOGGER | doc&project explain the G3 bootloader customizaiton(similar with G2) to run logger demo | https://community.nxp.com/t5/NXP-Designs-Knowledge-Base/S32G-Bootloader-G3-Customization/ta-p/176952... |

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Is there an English version of the supplemental document?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

你好,我正在调试mcu读写flash,我目前遇到A核启动到uboot阶段,norflash读写正常,但是到linux阶段,norflash功能会异常

uboot阶段 clk dump查看 qspi_flash2x是266666666

linux里dump /sys/kernel/debug/clk/clk_summary里qspi_flash2x是266666666然后变为0

查看dfs1寄存器,dfs1在被reset

请问这个问题如何定位

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

最终定位到问题为uboot 中board_common.c,在start kernel时board_cleanup_before_linux调用scmi_reset_agent导致,请问如果注释调会由什么影响