- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- RFID / NFC

- :

- NFC

- :

- PASS_THROUGH_MODE

PASS_THROUGH_MODE

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PASS_THROUGH_MODE

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

the recent weeks I've written NTAG I2C drivers for a new Cortex M4 MCU. Beside one issue everything works well.

The one tricky thing is how to get the SRAM_I2C_READY and the SRAM_RF_READY to be set to 1b. According to the spec sheet this should happen automatically considered PTHRU_DIR is defined and PTHRU_ON_OFF is set to 1b. Also the FD pin is activated.

All this is done, all this works, but when the MCU writes to the SRAM, or the Reader writes the the SRAM the respective SRAM_I2C_READY or SRAM_RF_READY never get set to 1b.

In PASS_THROUGH_MODE the SRAM gets activated in sector 1 and gets reduced to 16bytes overall. From F0 to FF. So, I have written one page to the SRAM from the RF side. I've also tried it with writing the whole block in a go to the SRAM from the RF side but SRAM_I2C_READY never gets set to 1b.

Any help appreciated.

Tom Fuerstner

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The size of the SRAM in NTAG I2C is not 16 bytes, but 64 bytes. From NFC side it is mapped as 16 pages, 4 bytes each. From I2C side it is mapped as 4 blocks, 16 bytes each.

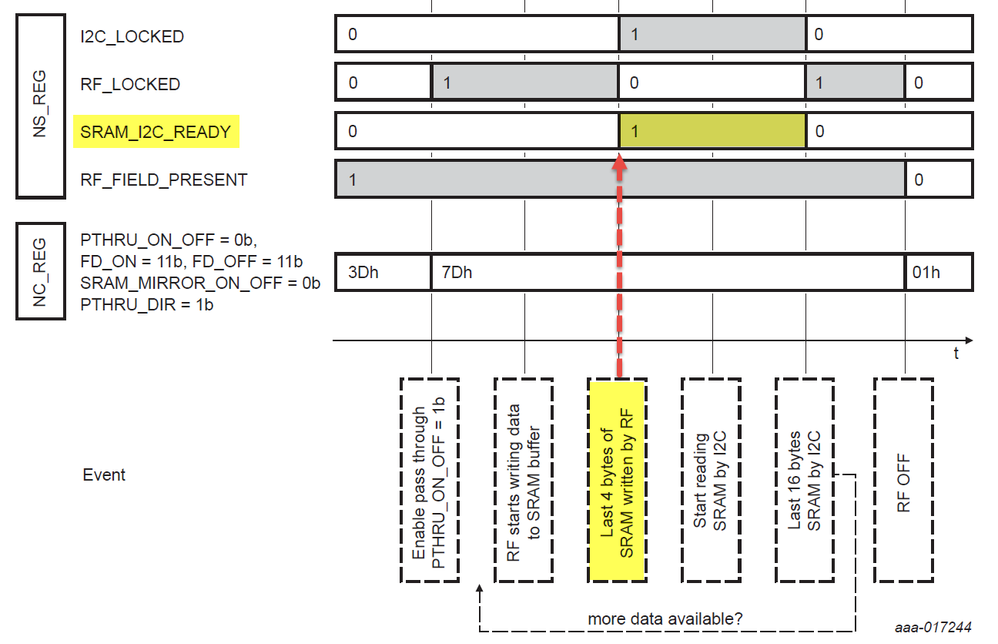

The SRAM_I2C_READY bit is only set after writing to the terminator page from the NFC side, i.e. page FF (last 4 bytes). See the next illustration from datasheet:

The attached presentation can also bring clarity about Pass-through mode.

Regards!

Jorge Gonzalez