Hello NXP team,

Currently we are working on SPI communication in MBDT Version 1.5.

And we are facing one issue: that we are getting one extra pulse in the serial clock pin before chip select goes low.

We can not able to decode this issue.

With this, we are facing challenges in reading SPI commands fro another ic.

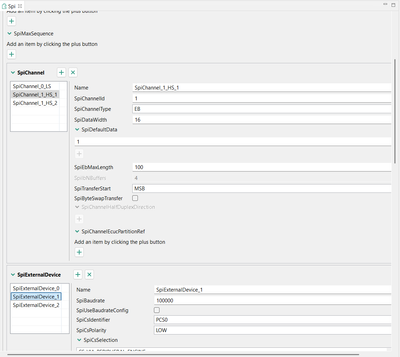

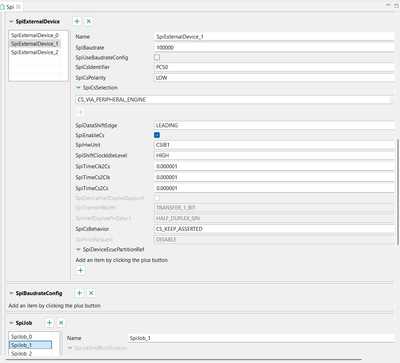

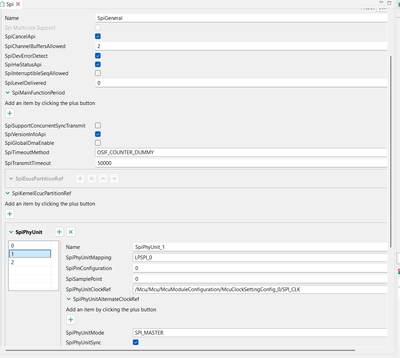

I have added the configuration photos which we done.

Kindly help us to resolve this issue ASAP.

@PetrS

@stefanvlad

@Irina_Costachescu

Thanks & Regards,

Vijay