- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 基于模型的设计工具箱(MBDT)

- :

- 基于模型的设计工具箱(MBDT)

- :

- SPI Config Block Requires Fixed Frame Size, MPC5775B Reference Design Requires Flexibility

SPI Config Block Requires Fixed Frame Size, MPC5775B Reference Design Requires Flexibility

We purchased the following board: MPC5775B BMS Plus VCU Reference Design

We started building a model in MBDT to exercise the inputs and outputs, many of which are driven by chips that communicate over a SPI interface with the MCU.

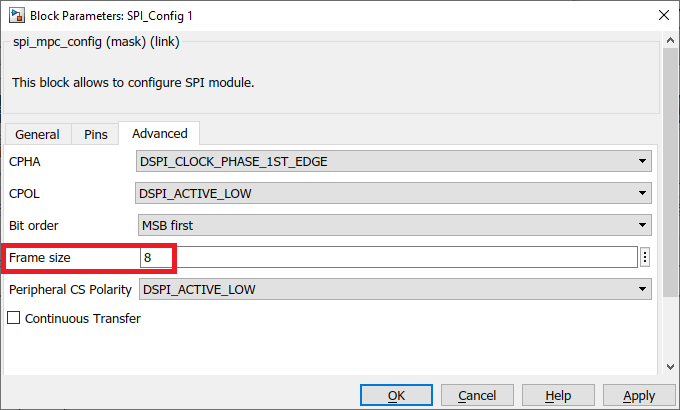

We noticed a problem where the SPI message frame size is set to a fixed size in the Config block, which implies it becomes hard-coded for the life of the application, see screenshot below.

The problem is that right away, we discover 3 chips that require 3 different frame sizes for SPI messages, and won't accept a set of 8-bit messages as an alternative:

The CD1030 (Multiple Switch Detection Interface) only accepts 32-bit frames.

The MC33996 (16-Oouptut Low-Side Switch) only accepts 24-bit frames.

The MC15XS3400 (Quad High-Side Switch) only accepts 16-bit frames.

Given this limitation, it seems the MBDT lacks the flexibility needed to create a fully functional application for the MPC5775B BMS Plus VCU Reference Design, though designs targeted to one chip at a time are certainly possible for demo or test.

The SPI message frame size needs the same flexibility we have with CAN messages, where the frame size of each message is chosen and can be different for each message sent.

Is this correct? Is there a work-around? I presume it would be hand-written C code.

已解决! 转到解答。

Hello @rsating

When you want to transfer more than 16 bits on a frame, you should enable the Continuous transfer.

This option will keep the CS low, over the entire frame that you want to send. Let's assume that you have two devices, the first one, connected to CS0, with a 32 bits frame, and the other one connected to CS1 with 24 bits frame.

To initiate a transfer with the first device, CS0, you have to provide to the SPI_Master_Transfer the 32 bits frame as an input of 4 uint8_t elements array. By having the Continuous transfer option checked the CS will remain low for 32 clock cycles, so 32-bit frame.

To transfer data to the second device, CS1, you have to provide to the SPI_Master_Transfer block an array of 3 uint8_T elements array.

In this way, you can address multiple devices with variable frame sizes.

Here you will find a similar question even this handles another MCU https://community.nxp.com/t5/NXP-Model-Based-Design-Tools/SPI-Message-for-32bit-Transfer-MPC5744P-MB...

Hope this helps,

Marius

Even if the frame size required by the three chips was not different, the Chip Select lines needed to address them in turn, one at a time, would have to be able to change, depending on which of the chips we communicate with. Is that possible? If not, it seems to prevent use of MBDT on boards that address multiple peripheral chips using the same SPI bus, as the MPC5775B Reference Design does.

The general pattern of Master-Slave SPI communication is that one Master can address many Slave devices. Is that possible with the MBDT? It seems we are constrained to 1 Master and 1 Slave. If that is not true, can we get guidance regarding how to proceed?

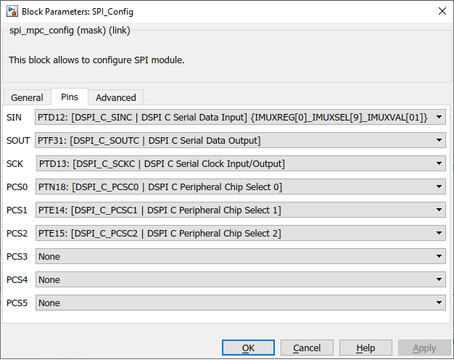

I found that MBDT does support multiple SPI Slave devices per Master, by specifying a CS pin per Slave as shown below:

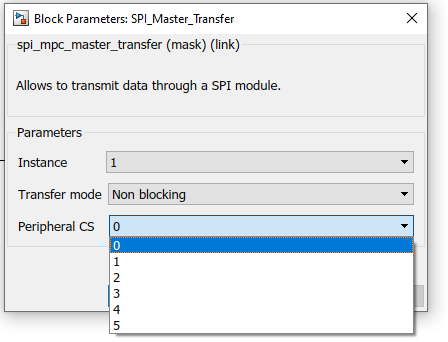

Then specifying the Peripheral CS in the SPI_Master_Transfer block:

However, the above block properties need to include a "Frame Size" field, because it is in general different for each slave device, as it is for chips of the MPC5775B Reference Design. Without this change, MBDT is not flexible enough for MPC5775B.

Hello @rsating

When you want to transfer more than 16 bits on a frame, you should enable the Continuous transfer.

This option will keep the CS low, over the entire frame that you want to send. Let's assume that you have two devices, the first one, connected to CS0, with a 32 bits frame, and the other one connected to CS1 with 24 bits frame.

To initiate a transfer with the first device, CS0, you have to provide to the SPI_Master_Transfer the 32 bits frame as an input of 4 uint8_t elements array. By having the Continuous transfer option checked the CS will remain low for 32 clock cycles, so 32-bit frame.

To transfer data to the second device, CS1, you have to provide to the SPI_Master_Transfer block an array of 3 uint8_T elements array.

In this way, you can address multiple devices with variable frame sizes.

Here you will find a similar question even this handles another MCU https://community.nxp.com/t5/NXP-Model-Based-Design-Tools/SPI-Message-for-32bit-Transfer-MPC5744P-MB...

Hope this helps,

Marius