- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

hi everyone,

I am working with MPC5775E board, using PAL lib, and I am trying to control eqADC with eDMA and triggering eqADC with PIT.

PIT generates interrupt and trigger eqADC properly, eDMA transfers command from system memory to CFIFO push register and also results are transferred from RFIFO to system memory by eDMA.

My question is that should I explicitly start eDMA channel to fill CFIFO by calling EDMA_DRV_StartChannel() function. I want to make eDMA automatically start to fill CFIFO. By the way I do not start RFIFO eDMA channel but it works fine. Can someone help me on this topic?

Best,

已解决! 转到解答。

I solved the issue.

While using SDK's eqADC driver init API disables eDMA request after transfer complete.

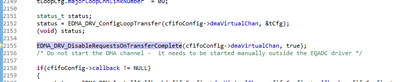

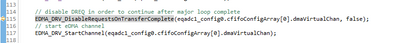

I disabled it by calling this function:

After this disable, eDMA works when eqADC requests to fill CFIFO and drain RFIFO.

I solved the issue.

While using SDK's eqADC driver init API disables eDMA request after transfer complete.

I disabled it by calling this function:

After this disable, eDMA works when eqADC requests to fill CFIFO and drain RFIFO.

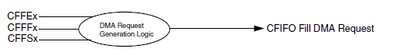

No, you should not trigger any DMA transfer manually. It is supposed to be triggered by eQADC module (by CFFFx and RFDFx flag).

If CFIFOx is not full DMA transfer is triggered by eQADC and loads one command to the CFIFO. If RFIFOx is not empty DMA transfer is triggered by eQADC and drains one result from the RFIFOx.